Manufacturability Aware Routing in Nanometer VLSI

# Manufacturability Aware Routing in Nanometer VLSI

# David Z. Pan

University of Texas USA dpan@cerc.utexas.edu

# Minsik Cho

IBM Research USA minsikcho@us.ibm.com

# Kun Yuan

University of Texas USA kyuan@cerc.utexas.edu

Boston – Delft

# Foundations and Trends<sup>®</sup> in Electronic Design Automation

Published, sold and distributed by: now Publishers Inc. PO Box 1024 Hanover, MA 02339 USA Tel. +1-781-985-4510 www.nowpublishers.com sales@nowpublishers.com

Outside North America: now Publishers Inc. PO Box 179 2600 AD Delft The Netherlands Tel. +31-6-51115274

The preferred citation for this publication is D. Z. Pan, M. Cho and K. Yuan, Manufacturability Aware Routing in Nanometer VLSI, Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol 4, no 1, pp 1–97, 2010

ISBN: 978-1-60198-350-3 © 2010 D. Z. Pan, M. Cho and K. Yuan

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers.

Photocopying. In the USA: This journal is registered at the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923. Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by now Publishers Inc for users registered with the Copyright Clearance Center (CCC). The 'services' for users can be found on the internet at: www.copyright.com

For those organizations that have been granted a photocopy license, a separate system of payment has been arranged. Authorization does not extend to other kinds of copying, such as that for general distribution, for advertising or promotional purposes, for creating new collective works, or for resale. In the rest of the world: Permission to photocopy must be obtained from the copyright owner. Please apply to now Publishers Inc., PO Box 1024, Hanover, MA 02339, USA; Tel. +1-781-871-0245; www.nowpublishers.com; sales@nowpublishers.com

now Publishers Inc. has an exclusive license to publish this material worldwide. Permission to use this content must be obtained from the copyright license holder. Please apply to now Publishers, PO Box 179, 2600 AD Delft, The Netherlands, www.nowpublishers.com; e-mail: sales@nowpublishers.com

# Foundations and Trends<sup>®</sup> in Electronic Design Automation Volume 4 Issue 1, 2010 Editorial Board

# Editor-in-Chief:

Sharad Malik Department of Electrical Engineering Princeton University Princeton, NJ 08544

# Editors

Robert K. Brayton (UC Berkeley) Raul Camposano (Synopsys) K.T. Tim Cheng (UC Santa Barbara) Jason Cong (UCLA) Masahiro Fujita (University of Tokyo) Georges Gielen (KU Leuven) Tom Henzinger (EPFL) Andrew Kahng (UC San Diego) Andreas Kuehlmann (Cadence Berkeley Labs) Ralph Otten (TU Eindhoven) Joel Phillips (Cadence Berkeley Labs) Jonathan Rose (University of Toronto) Rob Rutenbar (CMU) Alberto Sangiovanni-Vincentelli (UC Berkeley) Leon Stok (IBM Research)

# **Editorial Scope**

Foundations and Trends<sup>®</sup> in Electronic Design Automation will publish survey and tutorial articles in the following topics:

- System Level Design

- Behavioral Synthesis

- Logic Design

- Verification

- Test

- Physical Design

- Circuit Level Design

- Reconfigurable Systems

- Analog Design

# Information for Librarians

Foundations and Trends<sup>®</sup> in Electronic Design Automation, 2010, Volume 4, 4 issues. ISSN paper version 1551-3939. ISSN online version 1551-3947. Also available as a combined paper and online subscription.

Foundations and Trends<sup>®</sup> in Electronic Design Automation Vol. 4, No. 1 (2010) 1–97 © 2010 D. Z. Pan, M. Cho and K. Yuan DOI: 10.1561/1000000015

# Manufacturability Aware Routing in Nanometer VLSI

# David Z. Pan<sup>1</sup>, Minsik Cho<sup>2</sup> and Kun Yuan<sup>3</sup>

- <sup>1</sup> ECE Dept., University of Texas, Austin, TX 78712, USA, dpan@cerc.utexas.edu

- <sup>2</sup> Logic and Synthesis Dept., IBM Research, Yorktown Heights, NY 10598, USA, minsikcho@us.ibm.com

- <sup>3</sup> ECE Dept., University of Texas, Austin, TX 78712, USA, kyuan@cerc.utexas.edu

# Abstract

This monograph surveys key research challenges and recent results of manufacturability aware routing in nanometer VLSI designs. The manufacturing challenges have their root causes from various integrated circuit (IC) manufacturing processes and steps, e.g., deep sub-wavelength lithography, random defects, via voids, chemicalmechanical polishing, and antenna effects. They may result in both functional and parametric yield losses. The manufacturability aware routing can be performed at different routing stages including global routing, track routing, and detail routing, guided by both manufacturing process models and manufacturing-friendly rules. The manufacturability/yield optimization can be performed through both correct-by-construction (i.e., optimization during routing) and construct-by-correction (i.e., post-routing optimization). This monograph will provide a holistic view of key design for manufacturability issues in nanometer VLSI routing.

# Contents

| 1 Introduction                                                                                                                                                                                                                                                                                          | 1                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1.1 Major Manufacturability Issues                                                                                                                                                                                                                                                                      | 2                                       |

| 1.2 VLSI Routing Basics                                                                                                                                                                                                                                                                                 | 4                                       |

| 1.3 Rule vs. Model-Based Manufacturability Aware Routing                                                                                                                                                                                                                                                | 7                                       |

| 2 CMP Aware Routing                                                                                                                                                                                                                                                                                     | 11                                      |

| 2.1 CMP Modeling                                                                                                                                                                                                                                                                                        | 11                                      |

| 2.2 CMP Aware Global Routing                                                                                                                                                                                                                                                                            | 16                                      |

| 2.3 CMP Aware Full-Chip Routing                                                                                                                                                                                                                                                                         | 18                                      |

| 2.4 Summary                                                                                                                                                                                                                                                                                             | 20                                      |

|                                                                                                                                                                                                                                                                                                         |                                         |

| 3 Random-Defect Aware Routing                                                                                                                                                                                                                                                                           | <b>23</b>                               |

| <ul><li>3 Random-Defect Aware Routing</li><li>3.1 Critical Area Analysis and Modeling</li></ul>                                                                                                                                                                                                         | <b>23</b><br>23                         |

|                                                                                                                                                                                                                                                                                                         |                                         |

| 3.1 Critical Area Analysis and Modeling                                                                                                                                                                                                                                                                 | 23                                      |

| <ul><li>3.1 Critical Area Analysis and Modeling</li><li>3.2 Critical Area Minimization in Detailed/Post-routing</li></ul>                                                                                                                                                                               | $\begin{array}{c} 23\\ 26 \end{array}$  |

| <ul> <li>3.1 Critical Area Analysis and Modeling</li> <li>3.2 Critical Area Minimization in Detailed/Post-routing</li> <li>3.3 Critical Area Minimization in Global/Track Routing</li> </ul>                                                                                                            | 23<br>26<br>29                          |

| <ul> <li>3.1 Critical Area Analysis and Modeling</li> <li>3.2 Critical Area Minimization in Detailed/Post-routing</li> <li>3.3 Critical Area Minimization in Global/Track Routing</li> <li>3.4 Redundant Wire Insertion Techniques</li> </ul>                                                           | 23<br>26<br>29<br>30                    |

| <ul> <li>3.1 Critical Area Analysis and Modeling</li> <li>3.2 Critical Area Minimization in Detailed/Post-routing</li> <li>3.3 Critical Area Minimization in Global/Track Routing</li> <li>3.4 Redundant Wire Insertion Techniques</li> <li>3.5 Summary</li> </ul>                                      | 23<br>26<br>29<br>30<br>32              |

| <ul> <li>3.1 Critical Area Analysis and Modeling</li> <li>3.2 Critical Area Minimization in Detailed/Post-routing</li> <li>3.3 Critical Area Minimization in Global/Track Routing</li> <li>3.4 Redundant Wire Insertion Techniques</li> <li>3.5 Summary</li> <li>4 Lithography Aware Routing</li> </ul> | 23<br>26<br>29<br>30<br>32<br><b>33</b> |

| 4.4 Double Patterning Lithography Aware Routing         | 46 |

|---------------------------------------------------------|----|

| 4.5 PSM-Aware Routing                                   | 49 |

| 4.6 Summary                                             | 50 |

| 5 Redundant-Via Aware Routing                           | 53 |

| 5.1 Simultaneous Routing and Redundant Via Insertion    | 55 |

| 5.2 Post-routing Redundant Via Insertion                | 59 |

| 5.3 Wire Spreading for Enhanced Redundant               |    |

| Via Insertion                                           | 61 |

| 5.4 Various Redundant Via Derivatives                   | 64 |

| 5.5 Summary                                             | 66 |

| 6 Antenna-Effect Aware Routing                          | 69 |

| 6.1 Post-routing Optimization to Fix Antenna Violations | 70 |

| 6.2 Antenna-Effect Aware Routing                        | 73 |

| 6.3 Other Works                                         | 74 |

| 6.4 Summary                                             | 74 |

| 7 Other DFM Issues in VLSI Routing                      | 77 |

| 7.1 Multi-objective DFM Routing                         | 77 |

| 7.2 Dealing with Complex Manufacturing Rules            | 79 |

| 8 Conclusions                                           | 87 |

| References                                              | 91 |

Nanometer very large scale integrated (VLSI) circuit design faces tremendous challenges due to the manufacturing limitations. These manufacturing and process related challenges include the printability issues due to deep sub-wavelength lithography, the topography variations due to chemical-mechanical polishing (CMP), the random defects due to missing or extra material, and so on. Thus, the conventional design "closure" (on timing/noise, etc.) may not automatically guarantee the manufacturing closure due to the manufacturing yield loss. Manufacturability aware layout optimization plays a key role in the overall yield improvement.

In this monograph, we survey key aspects of manufacturability issues and how to alleviate them during the routing stage. There have been some design-for-manufacturability (DFM) efforts in earlier design stages such as logic synthesis and placement [41, 46, 89], yet routing is often considered one of the most critical stages in addressing the manufacturability issues due to the following reasons [24, 25, 26, 47, 86]: (1) many key manufacturing issues (e.g., topography variation due to chemical-mechanical polishing — CMP, random defects, printability due to optical lithography limitations, and so on) are tightly coupled

### 2 Introduction

with interconnects/wires which are mainly determined by routing; (2) routing is the last major VLSI physical design step before manufacturing, thus it has comprehensive picture of the physical layout needed to accurately estimate the overall manufacturability; (3) during routing it still has considerable flexibility to optimize and trade-off manufacturability and other conventional design objectives (e.g., timing, noise, power). These factors have led to very active academic and industrial research and development in *manufacturability aware routing*, which is the focus of this monograph.

The rest of the monograph will be organized as follows. Section 1 gives an overview of major manufacturability issues in nanometer VLSI designs, reviews the routing basics, and discusses various approaches to deal with manufacturability in routing. Then from Section 2 to Section 6, key manufacturability issues due to various process limitations will be discussed and dealt with through different manufacturability aware routing techniques, including CMP aware routing (Section 2), random-defect aware routing (Section 3), lithography aware routing (Section 4), redundant via aware routing (Section 5), and antenna-effect aware routing (Section 6). In Section 7, some more issues in manufacturability aware routing such as dealing with multiple DFM objectives and complicated design rules will be discussed, followed by summary and concluding remarks in Section 8.

## 1.1 Major Manufacturability Issues

In this section, we give an overview of major manufacturing issues which affect yield in nanometer designs (e.g., 65 nm technology node and below) [32, 100], and analyze their causes and effects, such as (1) printability issues due to sub-wavelength lithography system (i.e., feature size much smaller than the optical wavelength); (2) random defects due to missing or extra material; (3) topography variations due to chemical–mechanical polishing (CMP), and (4) other causes such as via failure and antenna effects.

(1) A fundamental limitation for the *sub-wavelength optical lithography* is WYSINWYG, i.e., "what you see (at design) is not what you get (at fab)". The printability issue arises between neighboring wires/vias

#### 1.1 Major Manufacturability Issues 3

due to sub-wavelength effects and process variations. As of today, the 193 nm wavelength optical lithography is still the dominant integrated circuit manufacturing process for 45 nm and 32 nm nodes. It is likely to remain so for 22 nm node or even below [106] due to delay in other viable next-generation lithography (e.g., extreme ultra-violet lithography — EUVL) and continued industry push in extending the 193 nm lithography through immersion lithography, resolution enhancement techniques (RET), and so on. However, if the initial design is very litho-unfriendly, even aggressive RET may not be able to solve the printability problem. Thus, the routing tool needs to construct litho-friendly and printable layouts.

As technology is further scaled down below 32 nm, the current single exposure immersion lithography is hit by the theoretical limit on feature resolution. As a candidate solution, EUVL with 13.5 nm wavelength has been researched heavily, targeting sub-32 nm technology nodes. However, the deployment of EUVL for commercial volume production has been delayed multiple times (due to light sources, material issues, mask fabrication, and so on), and is likely to be pushed out to the 16 nm node or below, if at all [33, 56, 62]. To bridge the gap between the current single exposure immersion lithography and EUV lithography, double patterning lithography (DPL) has received a lot of attention from industry. DPL is regarded as a technically and practically viable technology to achieve high resolution for 22 nm node [2, 49, 53, 62, 96, 104, 128]. However, the deployment of DPL needs to tackle two major challenges, layout decomposition and overlay error [2, 33, 56, 107], and routing and layout optimization can play a proactive role to mitigate them.

(2) Smaller feature size makes nanometer VLSI designs more vulnerable to random defects, which can be further divided into open or short defects [31, 61]. The back-end-of-line (BEOL) defects [57] may cause electrical opens or shorts on the interconnects. While it is generally believed that the yield loss due to systematic sources is greater than that due to random defects during the technology and process rampup stage, the systematic yield loss can be largely eliminated when the process becomes mature and systematic variations are ultimately compensated. On the other hand, the random defects which are inherent due to manufacturing limitations will still be there even for mature

#### 4 Introduction

fabrication process. Thus, its relative importance will indeed be bigger for mature process with systematic variations designed in [25].

(3) Topography (thickness) variation due to dishing and erosion after CMP is shown to be systematically determined by wire density distribution [37, 66, 101, 122, 142]. Even after CMP, intra-chip topography variation can still be in the order of 20–40% [42, 101]. Such topography variation leads to not only significant performance degradation due to increased wire resistance, but also acute manufacturing issues like etching and printability due to defocus [37, 42, 101, 122]. The main reason for the copper CMP problems is uneven wire density distribution. Higher wire density usually leads to copper thickness reduction due to erosion after CMP [66, 142], making resistance worse. Also, the reduced copper thickness after CMP can worsen the scattering effect, further increasing resistance [52]. The wire density distribution is directly affected by routing.

(4) Vias may fail due to various reasons such as random defects, electromigration, cut misalignment, and/or thermal stress-induced voiding effects. Redundant vias (or double vias) can be inserted during VLSI routing to make the vias more robust [134]. Redundant via insertion is known to be highly effective, leading to  $10-100 \times$  lower failure rate [11].

(5) During IC fabrication process, charges from plasma etching can be accumulated in long floating wires. Such charges may result in high currents to thin-oxide gates (i.e., Fowler-Nordheim tunneling current), and cause permanent damages to the gates. This is known as the *antenna effect* [82]. There are three kinds of solutions to resolve the antenna effect: protection diode embedding, diode insertion after placement and routing, and jumper insertion. While the first two solutions need extra area for diode, the jumper insertion incurs overhead in routing system due to additional vias [18].

These nanometer manufacturing issues will be addressed in manufacturability aware VLSI routing.

## 1.2 VLSI Routing Basics

Routing is a key step in integrated circuit physical design to connect signal nets together through geometrical embedding after block/cell

#### 1.2 VLSI Routing Basics 5

placement. Due to the complexity of routing, divide-and-conquer approach is usually used to make the problem size manageable, e.g., through global routing and detailed routing. Global routing divides the chip into global routing cells and plans approximate routing paths for global nets (i.e., the signal nets between different routing cells). Detailed routing follows the guidance from global routing and finalizes the exact geometrical embedding/routing for all nets while satisfying all the design rule checking (DRC). Track routing, as an intermediate step between global and detailed routing, can expedite detailed routing by embedding major trunks from each net within a panel (a row/column of global routing cells) in DRC-friendly manner [4].

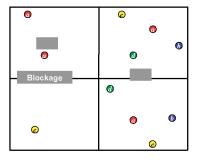

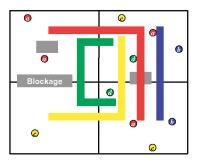

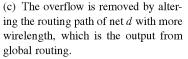

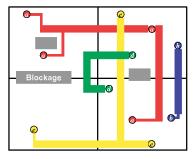

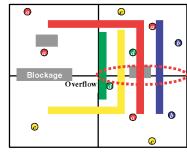

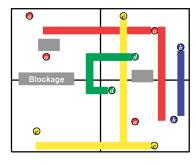

Figure 1.1 illustrates an example of modern routing systems [22, 23, 35, 73, 87, 91, 94, 103]. The input to the routing system is the legalized placement result where pins are not yet connected. The entire chip area is further dissected into global routing grid in order to reduce routing complexity as shown in Figure 1.1(a). Once partitioned properly into routing grids, the goal of global routing is to find a grid-to-grid routing path instead of pin-to-pin connection for each net. One possible global routing solution is shown in Figure 1.1(b). However, such solution could cause routing to be heavily congested and even unroutable. An alternative global routing solution is shown in Figure 1.1(c) where wires are more evenly distributed without any overflow [59, 127].

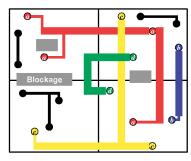

Once a global routing solution is fixed, track routing tunes the locations of wire pieces such that the wires can be more DRC friendly (e.g., connected to the pins, minimum spacing rules, and so on), while honoring the global routing decisions [4]. An example of track routing is shown in Figure 1.1(d) where wire pieces are placed such that maximum number of pins can be connected. Detailed routing follows the track routing solution to finalize all the electrical connections. Mainly, it performs local wiring to connect pins to wires (from track routing) as shown in Figure 1.1(e), or pins to pins for short wires (which are not considered during global routing) as in Figure 1.1(f). The final detailed routing solution should not have any electrical open or short in a DRC-clean manner. For difficult designs, these steps may need to be repeated in order to satisfy multiple design constraints (e.g., timing, power, noise, and so on) and reach the design closure.

## 6 Introduction

(a) After placement, the chip area is divided into global routing cells, with routing blockages in grey and four nets, a, b, c, and d.

(e) Detailed routing connects a pin to the nearest wire for each net in a DRC clean manner.

(b) A global routing solution where each net is routed in the shortest path, causing overBow (too many wires in a small region).

(d) Track routing tunes the location of each segment in a way that the distance from the corresponding pins is minimized, avoiding routing blockages.

(f) Detailed routing also completes local nets within each global routing grid.

Fig. 1.1 Illustration of a modern routing system which consists of three routing stages: global routing, track routing, and detailed routing.

#### 1.3 Rule vs. Model-Based Manufacturability Aware Routing 7

As seen from Figure 1.1, each routing stage has information on wire distribution, connectivity, and so on but at different levels of accuracy. For example, wire density distribution can be estimated as early as global routing with a high accuracy, and the spacing between majority of wires may be known during track routing. However, detailed wire shapes will be finalized only during detailed routing.

Depending on how a router places polygon shapes, a router can be classified into either *grid-based* routing or *gridless* routing [105]. In a grid-based routing system, polygons like vias or wires need to follow the underlying routing grid, thus only discrete wire widths and spacings such as  $1\times$ ,  $2\times$ ,  $3\times$ , and so on are available. A gridless router does not assume any underlying grid but directly manipulates the polygon shapes using some tile graph, thus it can have arbitrary width or spacing as long as the design rules are satisfied. In general, grid-based routing is more popular due to regular wire width, wire spacing, and faster runtime. On the other hand, gridless routing has more flexibility and solution space due to variable width and spacing. Thus, it could potentially achieve better solution quality. But the router complexity and runtime may be significantly higher [15, 30]. In a modern routing systems, a hybrid approach may be adopted, or a finer subgrid could be used to mimic a gridless router [75].

## 1.3 Rule vs. Model-Based Manufacturability Aware Routing

The approaches for manufacturing aware routing can be roughly classified into two groups: *rule-based* and *model-based*. The rule-based approach imposes additional manufacturability-driven design rules on a router to avoid manufacturability-unfriendly patterns. The modelbased approach utilizes some chip manufacturing process models to estimate the manufacturability/yield and guide the router. There are pros and cons for both rule-based and model-based approaches in terms of runtime, scalability, implementation, controllability, trade-off, etc.

Rule-based approach extends the conventional *design rules* paradigm, by imposing a new set of manufacturability friendly design rules provided by the fab. These new manufacturability aware rules can be *required/hard* rules, or *recommended/soft* rules. Since existing

### 8 Introduction

routing systems have been based on design rules for decades [85], the rule-based approach is friendly to the conventional design flow, which makes it seemingly easy to implement and apply. However, there are several serious challenges with rule-based approach.

- (1) The number of such manufacturability aware rules is increasing exponentially with the introduction of each new technology node. For example, while the number of rules is only a few dozen at 180 nm node, it reaches to several hundreds at 65 nm node.

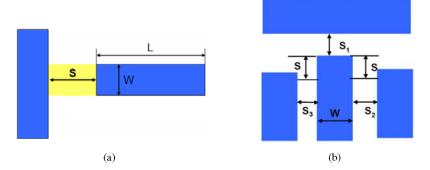

- (2) The complexity of ensuring these rules becomes more computationally expensive, as the rules are becoming more complicated and increasingly context-sensitive [29, 32, 74]. For example, the minimum spacing between wires may depend on the wire lengths and the neighborhood wires, as shown in an example in Figure 1.2. Therefore, simply checking

| Description                                                                                                                                                                                        | Rule (µm) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Minimum spacing (S) between a metal and the end-of-line of the metal whose edge width (W) $\leq 0.2~\mu m$                                                                                         | 0.14      |

| If a metal of width (W) $\leq$ 0.2 has neighboring metals along three adjacent edges, then one of the spacings (S <sub>1</sub> or S <sub>2</sub> or S <sub>3</sub> ) should be $\geq$ 0.14 $\mu$ m | 0.14      |

| Otherwise, minimum spacing                                                                                                                                                                         | 0.11      |

Fig. 1.2 A context-dependent minimum spacing rule in a 65 nm technology is shown [29]. There are more and more complicated rules like this in sub-65 nm designs.

### 1.3 Rule vs. Model-Based Manufacturability Aware Routing 9

rules would need considerable amount of computing resource. More examples of how to deal with these rules will be discussed in Section 7.2.

- (3) The rules are binary in nature, i.e., either following the rule or violating the rule, thus the rule-based approach does not provide smooth trade-off among different design objectives, such as timing, noise, area, and manufacturability.

- (4) The rules may be too restrictive and pessimistic. Sometimes, it may be infeasible to achieve the area or performance goal due to large guard-bands from these rules. For this reason, the restrictive design rules (RDR) [76, 77, 98, 129], which are widely used for transistor/poly layout, are not widely adopted for routing, as routing patterns can be extremely complicated. Furthermore, the rules themselves may not be accurate enough to model very complicated manufacturing processes, in particular for the future deeper sub-wavelength lithography processes.

Due to these limitations of the rule-based approach, there have been significant research efforts in the model-based manufacturability aware routing recently, expecting that models will capture the overall manufacturability more accurately and holistically at affordable computational overhead. A modern IC manufacturing system involves non-linear optical, chemical, electrical, and mechanical processes which could be extremely complicated to model accurately and efficiently. For example of lithography, the model needs to capture the process where light source will pass through a mask and react with photoresists on the wafer surface, and result in printed images. There are process variations involved, and various resolution enhancement techniques may be used. The challenge with model-based approach is how to abstract a set of reasonably accurate and high-fidelity models at various abstraction levels to guide physical layout optimizations. Meanwhile, the models have to be compact and efficient enough to be embedded in the already timeconsuming VLSI routing system. Therefore, a key technical bottleneck

# 10 Introduction

for model-based manufacturability aware routing is to develop simple yet high-fidelity models, and apply them at proper routing stages in a seamless manner with consideration of other routing objectives. The model-based approach can be coupled with a small set of required design rules.

- C. A. Allan, "Targeted layout modifications for semiconductor yield/reliability enhancement," in *IEEE Transactions on Semiconductor Manufacturing*, November 2004.

- [2] G. E. Bailey, A. Tritchkov, J.-W. Park, L. Hong, V. Wiaux, E. Hendrickx, S. Verhaegen, P. Xie, and J. Versluijs, "Double pattern EDA solutions for 32 nm HP and beyond," in *Proceedings of SPIE 6521*, 2007.

- [3] C. Bamji and E. Malavasi, "Enhanced network flow algorithm for yield optimization," in *Proceedings of Design Automation Conference*, 1996.

- [4] S. Batterywala, N. Shenoy, W. Nicholls, and H. Zhou, "Track assignment: A desirable intermediate step between global routing and detailed routing," in *Proceedings of International Conference on Computer Aided Design*, 2002.

- [5] P. Berman, A. B. Kahng, D. Vidhani, H. Wang, and A. Zelikovsky, "Optimal phase conflict removal for layout of dark field alternating phase shifting masks," in *Proceedings of International Symposium on Physical Design*, April 1999.

- [6] J. Bickford, M. Bühler, J. Hibbeler, J. Koehl, D. Müller, S. Peyer, and C. Schulte, "Yield improvement by local wiring redundancy," in *Proceedings* of International Symposium on Quality Electronic Design, March 2006.

- [7] J. Bickford, J. Hibbeler, M. Buhler, J. Koehl, D. Muller, S. Peyer, and C. Schulte, "Yield improvement by local wiring redundancy," in *Proceedings* of International Symposium on Quality Electronic Design, March 2006.

- [8] M. Born and E. Wolf, Principles of Optics: Electromagnetic Theory of Propagation, Interference and Diffraction of Light. Cambridge University Press, 7th ed., 1999.

- [9] CALIBRE, Mentor Graphics Corp.

- [10] F.-Y. Chang, R.-S. Tsay, and W.-K. Mak, "How to consider shorts and guarantee yield rate improvement for redundant wire insertion," in *Proceedings of International Conference on Computer Aided Design*, November 2009.

- [11] H.-Y. Chen, M.-F. Chiang, Y.-W. Chang, L. Chen, and B. Han, "Novel full-chip gridless routing considering double-via insertion," in *Proceedings of Design Automation Conference*, July 2006.

- [12] H.-Y. Chen, S.-J. Chou, S.-L. Wang, and Y.-W. Chang, "A novel wire-densitydriven full-chip routing system for CMP variation control," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 28, pp. 193–206, February 2009.

- [13] P. H. Chen, S. Malkani, C.-M. Peng, and J. Lin, "Fixing antenna problem by dynamic diode dropping and jumper insertion," in *Proceedings of International* Symposium on Quality Electronic Design, March 2000.

- [14] T.-C. Chen and Y.-W. Chang, "Routability-driven and optical proximity correction-aware multilevel full-chip gridless routing," *IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems*, vol. 26, 2007.

- [15] T.-C. Chen, Y.-W. Chang, and S.-C. Lin, "A novel framework for multilevel full-chip gridless routing," in *Proceedings of Asia and South Pacific Design Automation Conference*, December 2006.

- [16] T.-C. Chen, M. Cho, D. Z. Pan, and Y.-W. Chang, "Metal-density driven placement for CMP variation and routability," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 27, pp. 2145– 2155, December 2008.

- [17] T.-C. Chen, G.-W. Liao, and Y.-W. Chang, "Predictive formulae for OPC with applications to lithography-friendly routing," in *Proceedings of Design Automation Conference*, pp. 510–515, 2008.

- [18] Z. Chen and I. Koren, "Layer reassignment for antenna effect minimization in 3-layer channel routing," in *Proceedings of International Symposium Defect* and Fault-Tolerance in VLSI Systems, November 1996.

- [19] Z. Chen and I. Koren, "Layer reassignment for antenna effect minimization in 3-layer channel routing," in *Proceedings of IEEE International Symposium Defect Fault Tolerance*, November 1996.

- [20] J.-D. Cho, S. Raje, and M. Sarrafzadeh, "Fast approximation algorithms on Maxcut, k-coloring, and k-color ordering for VLSI applications," *IEEE Transactions on Computers*, vol. 47, no. 11, pp. 1253–1266, 1998.

- [21] M. Cho, Y. Ban, and D. Z. Pan, "Double patterning technology friendly detailed routing," in *Proceedings of International Conference on Computer Aided Design*, November 2008.

- [22] M. Cho, K. Lu, K. Yuan, and D. Z. Pan, "BoxRouter 2.0: Architecture and implementation of a hybrid and robust global router," in *Proceedings of International Conference on Computer Aided Design*, November 2007.

- [23] M. Cho and D. Z. Pan, "BoxRouter: A new global router based on box expansion and progressive ILP," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, pp. 2130–2143, December 2007.

- [24] M. Cho, H. Xiang, R. Puri, and D. Z. Pan, "Wire density driven global routing for CMP variation and timing," in *Proceedings of International Conference on Computer Aided Design*, November 2006.

- [25] M. Cho, H. Xiang, R. Puri, and D. Z. Pan, "TROY: Track routing and optimization for yield," *IEEE Transactions on Computer-Aided Design of Inte*grated Circuits and Systems, vol. 27, pp. 872–882, May 2008.

- [26] M. Cho, K. Yuan, Y. Ban, and D. Z. Pan, "ELIAD: Efficient lithography aware detailed routing algorithm with compact and macro post-OPC printability prediction," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 28, no. 7, pp. 1006–1016, 2009.

- [27] C. Christiansen, B. Li, J. Gill, R. Filippi, and M. Angyal, "Via-depletion electromigration in copper interconnects," in *IEEE Transactions on Device* and Materials Reliability, June 2006.

- [28] N. B. Cobb, "Fast optical and process proximity correction algorithms for integrated circuit manufacturing," Ph.D. Thesis, University of California, Berkeley, 1998.

- [29] J. Cong, "Advanced routing techniques for nanometer IC designs," in Proceedings of International Conference on Computer Aided Design, November 2006.

- [30] J. Cong, J. Fang, and K.-Y. Khoo, "DUNE: A multi-layer gridless routing system with wire planning," in *Proceedings of International Symposium on Physical Design*, 2000.

- [31] P. Cristie and J. P. de Gyvez, "Prelayout interconnect yield prediction," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 11, pp. 55–59, February 2003.

- [32] D. Cross, E. Nequist, and L. Scheffer, "A DFM aware, space based router," in Proceedings of International Symposium on Physical Design, March 2007.

- [33] M. Drapeau, V. Wiaux, E. Hendrickx, S. Verhaegen, and T. Machida, "Double patterning design split implementation and validation for the 32 nm node," in *Proceedings of SPIE 6521*, 2007.

- [34] M. Drapeau, V. Wiaux, E. Hendrickx, S. Verhaegen, and T. Machida, "Double patterning design split implementation and validation for the 32nm node," in *Proceedings of SPIE 6521*, 2007.

- [35] J.-R. Gao, P.-C. Wu, and T.-C. Wang, "A new global router for modern designs," in *Proceedings of Asia and South Pacific Design Automation Conference*, 2008.

- [36] X. Gao and L. Macchiarulo, "Enhancing double-patterning detailed routing with lazy coloring and within-path conflict avoidance," in *Proceedings of Design, Automation and Test in Europe*, 2010.

- [37] T. E. Gbondo-Tugbawa, "Chip-scale modeling of pattern dependencies in copper chemical mechanical polishing process," PhD thesis, Massachusetts Institute of Technology, 2002.

- [38] R. S. Ghaida, K. Doniger, and P. Zarkesh-ha, "Random yield prediction based on a stochastic layout sensitivity model," *IEEE Transactions on Semiconduc*tor Manufacturing, vol. 2, pp. 329–337, March 2009.

- [39] R. Glang, "Defect size distribution in VLSI chips," *IEEE Transactions on Semiconductor Manufacturing*, vol. 4, pp. 265–269, November 1991.

- [40] P. Gupta, A. B. Kahng, Y. Kim, and D. Sylvester, "Self-compensating design for focus variation," in *Proceedings of Design Automation Conference*, June 2005.

- [41] P. Gupta, A. B. Kahng, and C.-H. Park, "Detailed placement for improved depth of focus and CD control," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2005.

- [42] L. He, A. B. Kahng, K. Tam, and J. Xiong, "Design of integrated-circuit interconnects with accurate modeling of CMP," in *Proceedings of SPIE 5756*, March 2005.

- [43] T.-Y. Ho, Y.-W. Chang, and S.-J. Chen, "Multilevel routing with antenna avoidance," in *Proceedings of International Symposium on Physical Design*, April 2004.

- [44] http://web.mit.edu/cmp/.

- [45] http://www.cadence.com/products/mfg/cmp-predictor/.

- [46] S. Hu and J. Hu, "Pattern sensitive placement for manufacturability," in Proceedings of International Symposium on Physical Design, March 2007.

- [47] L. Huang and D. F. Wong, "Optical proximity correction (OPC)-friendly maze routing," in *Proceedings of Design Automation Conference*, June 2004.

- [48] L.-D. Huang, X. Tang, H. Xiang, M. D. F. Wong, and I.-M. Liu, "A polynomial time-optimal diode insertion/routing algorithm for fixing antenna problem," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Sys*tems, vol. 23, pp. 141–147, January 2004.

- [49] J. Huckabay, W. Staud, R. Naber, A. van Oosten, P. Nikolski, S. Hsu, R. J. Socha, M. V. Dusa, and D. Flagello, "Process results using automatic pitch decomposition and double patterning technology (DPT) at  $k_{1eff} < 0.20$ ," in *Proceedings of SPIE 6349*, 2006.

- [50] E. P. Huijbregtz, H. Xue, and J. A. Jess, "Routing for reliable manufacturing," *IEEE Transactions on Semiconductor Manufacturing*, vol. 8, pp. 188–194, May 1995.

- [51] T. Iizuka, M. Ikeda, and K. Asada, "Exact wiring fault minimization via comprehensive layout synthesis for CMOS logic cells," in *Proceedings of International Symposium on Quality Electronic Design*, March 2004.

- [52] S. Im, N. Srivastava, K. Banerjee, and K. E. Goodson, "Scaling analysis of multilevel interconnect temperatures for high-performance ICs," *IEEE Transactions on Electron Devices*, vol. 52, pp. 2710–2719, December 2005.

- [53] Y. Inazuki, N. Toyama, T. Nagai, T. Sutou, Y. Morikawa, H. Mohri, N. Hayashi, M. Drapeau, K. Lucas, and C. Cork, "Decomposition difficulty analysis for double patterning and the impact on photomask manufacturability," in *Proceedings of SPIE 6925*, 2008.

- [54] Y. Jia, Y. Cai, and X. Hong, "Full-chip routing system for reducing Cu CMP & ECP variation," in *Proceedings of Annual Symposium on Integrated Circuits* and System Design, 2008.

- [55] Z.-W. Jiang and Y.-W. Chang, "An optimal simultaneous diode/jumper insertion algorithm for antenna fixing," in *Proceedings of International Conference* on Computer Aided Design, April 2006.

- [56] A. B. Kahng, "Key directions and a roadmap for electrical design for manufacturability," in *Proceedings of European Solid-State Circuits Conference*, 2007.

- [57] A. B. Kahng, B. Liu, and I. I. Mandoiu, "Non-tree routing for reliability and yield improvement," in *Proceedings of International Conference on Computer Aided Design*, November 2002.

- [58] A. B. Kahng and K. Samadi, "CMP fill synthesis: A survey of recent practice," *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems, vol. 27, pp. 3–19, January 2008.

- [59] R. Kastner, E. Bozorgzadeh, and M. Sarrafzadeh, "Pattern routing: Use and theory for increasing predictability and avoiding coupling," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 21, pp. 777–790, July 2002.

- [60] T. Kong, H. Leung, V. Raghavan, A. K. Wong, and S. Xu, "Model-assisted routing for improved lithography robustness," in *Proceedings of SPIE 6521*, 2007.

- [61] I. Koren, "Should yield be a Design objective?," in *Proceedings of International Symposium on Quality Electronic Design*, March 2000.

- [62] Y. Ku, "Lithography challenges and solution for 32 nm node and beyond," in Proceedings of Asia and South Pacific Design Automation Conference, January 2008.

- [63] S.-Y. Kuo, "YOR: A yield-optimizing routing algorithm by minimizing critical areas and vias," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 12, pp. 1303–1311, September 1993.

- [64] J.-Y. Lai, N. Saka, and J. H. Chun, "Evolution of copper-oxide damascene structures in chemical mechanical polishing, — Copper dishing and oxide erosion," *Journal of The Electrochemical Society*, vol. 149, pp. G41–G50, 2002.

- [65] S. Lakshminarayanan, P. Wright, and J. Pallinti, "Electrical characterization of the copper CMP process and derivation of metal layout rules," *IEEE Transactions on Semiconductor Manufacturing*, vol. 16, November 2003.

- [66] S. Lakshminarayanan, P. J. Wright, and J. Pallinti, "Electrical characterization of the copper CMP process and derivation of metal layout rules," *IEEE Transactions on Semiconductor Manufacturing*, vol. 16, pp. 668–676, November 2003.

- [67] K.-Y. Lee, C.-K. Koh, T.-C. Wang, and K.-Y. Chao, "Optimal post-routing redundant via insertion," in *Proceedings of International Symposium on Physical Design*, April 2008.

- [68] K.-Y. Lee, S.-T. Lin, and T.-C. Wang, "Redundant via insertion with wire bending," in *Proceedings of International Symposium on Physical Design*, March 2009.

- [69] K.-Y. Lee and T.-C. Wang, "Post-routing redundant via insertion for yield/reliability improvement," in *Proceedings of Asia and South Pacific Design Automation Conference*, 2006.

- [70] K.-Y. Lee, T.-C. Wang, and K.-Y. Chao, "Post-routing redundant via insertion and line end extension with via density consideration," in *Proceedings of International Conference on Computer Aided Design*, November 2006.

- [71] LEF/DEF Reference Manual version 5.7.

- [72] C.-K. Lei, P.-Y. Chiang, and Y.-M. Lee, "Post-routing redundant via insertion with wire spreading capability," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2009.

- [73] H. K.-S. Leung, "Advanced routing in changing technology landscape," in Proceedings of International Symposium on Physical Design, pp. 118–121, ACM Press, 2003.

- [74] H. K.-S. Leung, "Advanced routing in changing technology landscape," in Proceedings of International Symposium on Physical Design, 2003.

- [75] H. K.-S. Leung and R. X. Nijssen, Subgrid Detailed Routing. U.S. Patent, 6507941 B1, Jan. 14, 2003.

- [76] L. W. Liebmann, "Resolution enhancement techniques in optical lithography: It's not just a mask problem," in *Proceedings of SPIE* 4409, pp. 23–32, September 2001.

- [77] L. W. Liebmann, "Layout impact of resolution enhancement techniques: Impediment or opportunity?," in *Proceedings of International Symposium on Physical Design*, 2003.

- [78] C.-T. Lin, Y.-H. Lin, G.-C. Su, and Y.-L. Li, "Dead via minimization by simultaneous routing and redundant via insertion," in *Proceedings of Asia* and South Pacific Design Automation Conference, January 2010.

- [79] K. Lucas, C. Cork, A. Miloslavsky, G. Luk-Pat, L. Barnes, J. Hapli, J. Lewellen, G. Rollins, V. Wiaux, and S. Verhaegen, "Interactions of double patterning technology with wafer processing, OPC and design flows," in *Proceedings of SPIE 6924*, 2008.

- [80] F. Luo, Y. Jia, and W. W.-M. Dai, "Yield-preferred via insertion based on novel geotopological technology," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2006.

- [81] W. Maly, "Modeling of lithography related yield losses for CAD of VLSI circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 4, pp. 166–177, July 1985.

- [82] W. Maly, C. Ouyang, S. Ghosh, and S. Maturi, "Detection of an antenna effect in VLSI designs," in *Proceedings of International Symposium Defect* and Fault-Tolerance in VLSI Systems, November 1996.

- [83] K. McCullen, "Phase correct routing for alternating phase shift masks," in Proceedings of Design Automation Conference, 2004.

- [84] K. McCullen, "Redundant via insertion in restricted topology layout," in Proceedings of International Symposium on Quality Electronic Design, March 2007.

- [85] C. Mead and L. Conway, Introduction to VLSI Systems. Addison-Wesley, 1980.

- [86] J. Mitra, P. Yu, and D. Z. Pan, "RADAR: RET-aware detailed routing using fast lithography simulations," in *Proceedings of Design Automation Confer*ence, June 2005.

- [87] M. D. Moffitt, J. A. Roy, and I. L. Markov, "The coming of age of (Academic) global routing," in *Proceedings of International Symposium on Physical Design*, pp. 148–155, 2008.

- [88] D. Muller, "Optimizing yield in global routing," in Proceedings of International Conference on Computer Aided Design, 2006.

- [89] A. Nardi and A. L. Sangiovanni-Vincentelli, "Logic synthesis for manufacturability," in *IEEE Design & Test of Computers*, May 2004.

- [90] K. Noh, N. Saka, and J.-H. Chun, "A mechanical model for erosion in copper chemical mechanical polishing," in *Chemical-Mechanical Planarization for* ULSI Multilevel Interconnect Conference, 2003.

- [91] M. M. Ozdal and M. D. F. Wong, "ARCHER: A history-driven global routing algorithm," in *Proceedings of International Conference on Computer Aided Design*, November 2007.

- [92] D. Z. Pan, M. Cho, K. Yuan, and Y. Ban, "Lithography friendly routing: From construct-by-correction to correct-by-construction," in *International Confer*ence on Solid-State and Integrated-Circuit Technology, October 2008.

- [93] D. Z. Pan and M. D. F. Wong, "Manufacturability-aware physical layout optimizations," in *Proceedings of International Conference on Integrated Circuit Design and Technology*, May 2005.

- [94] M. Pan and C. Chu, "FastRoute: A step to integrate global routing into placement," in Proceedings of International Conference on Computer Aided Design, 2006.

- [95] E. Papadopoulou and D. T. Lee, "Critical area computation via voronoi diagrams," *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems, vol. 18, pp. 463–474, April 1999.

- [96] J. Park, S. Hsu, D. V. D. Broeke, J. F. Chen, M. Dusa, R. Socha, J. Finders, B. Vleeming, A. van Oosten, P. Nikolsky, V. Wiaux, E. Hendrickx, J. Bekaert, and G. Vandenberghe, "Application challenges with double patterning technology (DPT) beyond 45 nm," in *Proceedings of SPIE 6349*, 2006.

- [97] Y. Pati, A. Ghazanfarian, and R. Pease, "Exploiting structure in fast aerial image computation for integrated circuit patterns," *IEEE Transactions on Semiconductor Manufacturing*, vol. 10, pp. 62–74, February 1997.

- [98] R. F. Pease, "Lithographic technologies that haven't (yet) made it: Lessons learned (Plenary Paper)," in *Proceedings of SPIE 5751*, pp. 15–25, May 2005.

- [99] A. Pitaksanonku, S. Thanawastien, C. Lursinsap, and J. Gandhi, "DTR: A defect-tolerant routing algorithm," in *Proceedings of Design Automation Conference*, 1989.

- [100] R. Puri, "Design and CAD challenges for 45 nm and beyond," in *Proceedings* of International Conference on Computer Aided Design, November 2006.

- [101] X. Qi, A. Gyure, Y. Luo, S. C. Lo, M. Shahram, and K. Singhal, "Emerging technologies: Measurement and characterization of pattern dependent process variations of interconnect resistance, capacitance and inductance in nanometer technologies," in ACM Great Lakes Symposium on VLSI, April 2006.

- [102] O. Rizzo and H. Melzner, "Concurrent wire spreading, widening, and filling," in Proceedings of Design Automation Conference, July 2007.

- [103] J. A. Roy and I. L. Markov, "High-performance routing at the nanometer scale," *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems, pp. 1066–1077, June 2008.

- [104] J. Rubinstein and A. Neureuther, "Post-decomposition assessment of double patterning layouts," in *Proceedings of SPIE 6924*, 2008.

- [105] W. L. Schiele, T. Krüger, K. M. Just, and F. H. Kirsch, "A gridless router for industrial design rules," in *Proceedings of Design Automation Conference*, 1990.

- [106] Semiconductor Industry Association, International Technology Roadmap for Semiconductors. 2009. http://public.itrs.net/.

- [107] A. Sezginer and B. Yenikaya, "Double patterning technology: Process-window analysis in a many-dimensional space," in *Proceedings of SPIE 6521*, 2007.

- [108] Y. Shen, Y. Cai, Q. Zhou, and X. Hong, "DFM based detailed routing algorithm for ECP and CMP," in *Proceedings of International Symposium on Quality Electronic Design*, March 2008.

- [109] H. Shirota, T. Sadakane, and M. Terai, "A new rip-up and reroute algorithm for very large scale gate arrays," in *Proceedings of IEEE Custom Integrated Circuits Conference*, May 1996.

- [110] H. Shirota, T. Sadakane, M. Terai, and K. Okazaki, "A new router for reducing antenna effect in ASIC design," in *Proceedings of IEEE Custom Integrated Circuits Conference*, May 1998.

- [111] S. Sinha, J. Luo, and C. Chiang, "Model based layout pattern dependent metal filling algorithm for improved chip surface uniformity in the copper process," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2007.

- [112] S. Sinha, Q. Su, L. Wen, F. Lee, C. Chiang, Y.-K. Cheng, J.-L. Lin, and Y.-C. Harn, "A new flexible algorithm for random yield improvement," in *Proceedings of International Symposium on Quality Electronic Design*, March 2007.

- [113] C. Spence, "Full-chip lithography simulation and design analysis: How OPC is changing IC design," in *Proceedings of SPIE 5751*, pp. 1–14, 2005.

- [114] B.-Y. Su and Y.-W. Chang, "An exact jumper insertion algorithm for antenna effect avoidance/fixing," in *Proceedings of Design Automation Conference*, June 2005.

- [115] B.-Y. Su and Y.-W. Chang, "An exact jumper-insertion algorithm for antenna violation avoidance/fixing considering routing obstacles," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, April 2007.

- [116] B.-Y. Su and Y.-W. Chang, "An optimal jumper-insertion algorithm for antenna avoidance/fixing," in *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, October 2007.

- [117] B.-Y. Su, Y.-W. Chang, and J. Hu, "An optimal jumper insertion algorithm for antenna avoidance/fixing on general routing trees with obstacles," in *Proceedings of International Symposium on Physical Design*, November 2006.

- [118] J. Su and W. Dai, "Post-route optimization for improved yield using a rubberband wiring model," in *Proceedings of International Conference on Computer Aided Design*, 1997.

- [119] J. Z. Su and W. Dai, "Post route optimization for improved yield using a rubber-band wiring model," in *Proceedings of International Conference on Computer Aided Design*, pp. 700–706, November 1997.

- [120] Taiwan Semiconductor Manufacturing Company (TSMC). Reference Flow 5.0 and Reference Flow 6.0.

- [121] M.-C. Tasi, Y.-C. Lin, and T.-C. Wang, "An MILP-based wire spreading algorithm for PSM-aware layout modification," in *Proceedings of Asia and South Pacific Design Automation Conference*, 2008.

- [122] R. Tian, D. F. Wong, and R. Boone, "Model-based dummy feature placement for oxide chemical-mechanical polishing manufacturability," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 20, pp. 902–910, July 2001.

- [123] Y.-S. Tong, C.-W. Lin, and S.-J. Chen, "An automatic optical-simulationbased lithography hotspot fix flow for post-route optimization," in *Proceedings* of International Symposium on Physical Design, 2009.

- [124] C.-C. Tsai, F.-T. Hsu, C.-C. Kuo, J.-O. Wu, and T.-Y. Lee, "X-clock tree construction for antenna avoidance," in *International Conference on Solid-State and Integrated-Circuit Technology*, October 2008.

- [125] J. Wang and H. Zhou, "Optimal jumper insertion for antenna avoidance under ratio upperbound," in *Proceedings of Design Automation Conference*, July 2006.

- [126] L.-C. Wei, H.-M. Chen, L.-D. Huang, and S. S. Xu, "Efficient and optimal post-layout double-cut via insertion by network relaxation and min-cost maximum flow," in ACM Great Lakes Symposium on VLSI, May 2008.

- [127] J. Westra, P. Groeneveld, T. Yan, and P. H. Madden, "Global routing: Metrics, benchmarks, and tools," in *IEEE DATC Electronic Design Process*, April 2005.

- [128] V. Wiaux, S. Verhaegen, S. Cheng, F. Iwamoto, P. Jaenen, M. Maenhoudt, T. Matsuda, S. Postnikov, and G. Vandenberghe, "Split and design guidelines for double patterning," in *Proceedings of SPIE 6924*, 2008.

- [129] A. K. Wong, "Microlithography: Trends, challenges, solutions, and their impact on design," *IEEE Micro*, vol. 23, December 2003.

- [130] D. Wu, J. Hu, and R. Mahapatra, "Coupling aware timing optimization and antenna avoidance in layer assignment," in *Proceedings of International Symposium on Physical Design*, April 2005.

- [131] D. Wu, J. Hu, and R. Mahapatra, "Antenna avoidance in layer assignment," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 25, pp. 734–774, April 2006.

- [132] Y.-R. Wu, M.-C. Tsai, and T.-C. Wang, "Maze routing with OPC consideration," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2005.

- [133] H. Xiang, L. Deng, R. Puri, K.-Y. Chao, and M. D. F. Wong, "Fast dummy-fill density analysis with coupling constraints," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 27, pp. 633–642, April 2008.

- [134] G. Xu, R. Tian, D. Z. Pan, and M. D. F. Wong, "CMP aware shuttle mask floorplanning," in *Proceedings of Asia and South Pacific Design Automation Conference*, January 2005.

- [135] J. Xu, S. Sinha, and C. C. Chiang, "Accurate detection for process-hotspots with vias and incomplete specification," in *Proceedings of International Conference on Computer Aided Design*, November 2007.

- [136] J.-T. Yan and Z.-W. Chen, "Redundant wire insertion for yield improvement," in ACM Great Lakes Symposium on VLSI, May 2009.

- [137] H. Yao, Y. Cai, Q. Zhou, and X. Hong, "Improved multilevel routing with redundant via placement for yield improvement," in ACM Great Lakes Symposium on VLSI, May 2005.

- [138] H. Yao, S. Sinha, C. Chiang, X. Hong, and Y. Cai, "Efficient process-hotspot detection using range pattern matching," in *Proceedings of International Conference on Computer Aided Design*, November 2006.

- [139] T. Yoshimura and E. Kuh, "Efficient algorithms for channel routing," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 1, pp. 25–35, January 1982.

- [140] P. Yu, S. X. Shi, and D. Z. Pan, "Process variation aware OPC with variational lithography modeling," in *Proceedings of Design Automation Conference*, July 2006.

- [141] K. Yuan, K. Lu, and D. Z. Pan, "Double patterning lithography friendly detailed routing with redundant via consideration," in *Proceedings of Design Automation Conference*, July 2009.

- [142] P. Zarkesh-Ha, S. Lakshminarayann, K. Doniger, W. Loh, and P. Wright, "Impact of interconnect pattern density information on a 90 nm technology ASIC design flow," in *Proceedings of International Symposium on Quality Electronic Design*, November 2003.