Full text available at: https://nowpublishers.com/EDA

Harnessing the Potential of Deep-learning Algorithms and Generative AI for SoC and Chiplet Design and Verification

## Other titles in Foundations and $\operatorname{Trends}^{\scriptscriptstyle{(\!\!\!\!\)}}$ in Electronic Design Automation

Polynomial Formal Verification of Arithmetic Circuits Alireza Mahzoon and Rolf Drechsler ISBN: 978-1-63828-404-8

Cloud and Edge Computing for Connected and Automated Vehicles Qi Zhu, Bo Yu, Ziran Wang, Jie Tang, Qi Alfred Chen, Zihao Li, Xiangguo Liu, Yunpeng Luo and Lingzi Tu ISBN: 978-1-63828-302-7

From CNN to DNN Hardware Accelerators: A Survey on Design, Exploration, Simulation, and Frameworks Leonardo Rezende Juracy, Rafael Garibotti and Fernando Gehm Moraes ISBN: 978-1-63828-162-7

Self-Powered Wearable IoT Devices for Health and Activity Monitoring Ganapati Bhat, Ujjwal Gupta, Yigit Tuncel, Fatih Karabacak, Sule Ozev and Umit Y. Ogras ISBN: 978-1-68083-748-3

On-Chip Dynamic Resource Management

Antonio Miele, Anil Kanduri, Kasra Moazzemi, Dávid Juhász, Amir R. Rahmani, Nikil Dutt, Pasi Liljeberg and Axel Jantsch ISBN: 978-1-68083-578-6

Smart Healthcare

Hongxu Yin, Ayten Ozge Akmandor, Arsalan Mosenia and Niraj K. Jha ISBN: 978-1-68083-440-6

## Harnessing the Potential of Deep-learning Algorithms and Generative AI for SoC and Chiplet Design and Verification

Edited by Imed Ben Dhaou Hannu Tenhunen Ahmed Abdelgawad Sree Ranjani Rajendran Rajat Subhra Chakraborty

# Foundations and Trends<sup>®</sup> in Electronic Design Automation

Published, sold and distributed by: now Publishers Inc. PO Box 1024 Hanover, MA 02339 United States Tel. +1-781-985-4510 www.nowpublishers.com sales@nowpublishers.com

Outside North America: now Publishers Inc. PO Box 179 2600 AD Delft The Netherlands Tel. +31-6-51115274

The content of the book was originally published in Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol. 14, no. 4.

ISBN: 978-1-63828-538-0 © 2025 Now Publishers Inc

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers.

Photocopying. In the USA: This journal is registered at the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923. Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by now Publishers Inc for users registered with the Copyright Clearance Center (CCC). The 'services' for users can be found on the internet at: www.copyright.com

For those organizations that have been granted a photocopy license, a separate system of payment has been arranged. Authorization does not extend to other kinds of copying, such as that for general distribution, for advertising or promotional purposes, for creating new collective works, or for resale. In the rest of the world: Permission to photocopy must be obtained from the copyright owner. Please apply to now Publishers Inc., PO Box 1024, Hanover, MA 02339, USA; Tel. +1 781 871 0245; www.nowpublishers.com; sales@nowpublishers.com

now Publishers Inc. has an exclusive license to publish this material worldwide. Permission to use this content must be obtained from the copyright license holder. Please apply to now Publishers, PO Box 179, 2600 AD Delft, The Netherlands, www.nowpublishers.com; e-mail: sales@nowpublishers.com

## Foundations and Trends<sup>®</sup> in Electronic Design Automation

Volume 14, Issue 4, 2025 Editorial Board

#### **Editor-in-Chief**

Axel Jantsch TU Wien

#### Editors

Bashir Al-Hashimi King's College London

Jason Cong University of California, Los Angeles

Andreas Gerstlauer The University of Texas at Austin

Christoph Grimm TU Kaiserslautern

Ahmed Jerraya $C\!E\!A\text{-}Leti$

Wolfgang Müller University of Paderborn

Partha Pande Washington State University Zebo Peng Linköping University

Christian Pilato Politecnico di Milano

Jaan Raik Tallinn University of Technology

Alberto Sangiovanni-Vincentelli University of California, Berkeley

Rishad Shafik Newcastle University

Sandeep Shukla Indian Institute of Technology, Kanpur

Norbert Wehn University of Kaiserslautern

### **Editorial Scope**

Foundations and Trends<sup>®</sup> in Electronic Design Automation publishes survey and tutorial articles in the following topics:

- System Level Design

- Behavioral Synthesis

- Logic Design

- Verification

- Test

- Physical Design

- Circuit Level Design

- Reconfigurable Systems

- Analog Design

- Embedded software and parallel programming

- Multicore, GPU, FPGA, and heterogeneous systems

- Distributed, networked embedded systems

- Real-time and cyberphysical systems

### Information for Librarians

Foundations and Trends<sup>®</sup> in Electronic Design Automation, 2025, Volume 14, 4 issues. ISSN paper version 1551-3939. ISSN online version 1551-3947. Also available as a combined paper and online subscription.

## Contents

| Editorial                                                                                                                                                                                                                          | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Deep Learning and Generative AI for Monolithic and Chiplet SoC<br>Design and Verification: A Survey<br>Imed Ben Dhaou, Syhem Larguech, Sree Ranjani Rajendran,<br>Rajat Subhra Chakraborty, Hannu Tenhunen and Ahmed<br>Abdelgawad | 4  |

| Large Language Models for EDA: From Assistants to Agents<br>Zhuolun He, Yuan Pu, Haoyuan Wu, Yuhan Qin, Tairu Qiu and<br>Bei Yu                                                                                                    | 54 |

| Evaluating Large Language Models for Automatic Register<br>Transfer Logic Generation for Combinational Circuits via<br>High-Level Synthesis<br>Sneha Swaroopa, Rijoy Mukherjee, Anushka Debnath and Rajat<br>Subhra Chakraborty    | 74 |

| Biographies                                                                                                                                                                                                                        | 97 |

### Editorial

The rapid advancements in semiconductor technology have significantly increased integration density, with modern System-on-Chip (SoC) designs for high-performance computing now exceeding 10 billion transistors. However, as we enter the nanometer regime, the traditional CMOS transistor scaling law has reached its physical limits. This has necessitated the adoption of More-than-Moore (MtM) technology, which integrates novel design methodologies and heterogeneous computing architectures.

Electronic Design Automation (EDA), design reuse, and IP-based methodologies have been instrumental in bridging the productivity gap, reducing time-to-market, and meeting increasingly stringent performance and security requirements. As electronic systems grow in complexity, new design and verification methodologies are emerging to address these challenges effectively.

In the pre-Internet of Things (IoT) era, the security of SoC designs was often an afterthought. However, the widespread adoption of IoT devices has made security a critical concern at every level of deployment. Current EDA tools, while optimizing for performance, inadvertently introduce vulnerabilities that expose circuits to threats such as side-channel attacks, reverse engineering, and hardware Trojans. This increasing focus on security necessitates the development of security-aware EDA tools capable of addressing threats such as fault injection, information leakage, and timing and power-based attacks. 2

Chiplet technology has evolved from tiled silicon architectures, where processors are divided into clusters to enhance signal propagation, to more advanced configurations where multiple processing elements, including RISC-V cores and application-specific co-processors, are integrated into chiplets. These chiplets leverage various interconnection methods, including 3D stacking and wafer-scale integration, utilizing flexible communication networks such as packet-switched and circuitswitched architectures. However, this shift to chiplet-based architectures presents new challenges in performance estimation and system validation due to the complexity of interconnects and heterogeneous integration.

Deep learning algorithms and Large Language Models (LLMs) have emerged as promising solutions to address the growing challenges in SoC and chiplet design and verification. The application of AI-driven methodologies is revolutionizing RTL generation, hardware security, and design automation, leading to enhanced power-performance-area (PPA) metrics and improved verification efficiency.

This special issue features three works that explore the transformative role of AI in EDA and SoC design:

- 1. Deep Learning and Generative AI for Monolithic and Chiplet SoC Design and Verification: A Survey delves into the impact of deep learning and generative AI, particularly LLMs like GPT, on SoC and chiplet architectures. It highlights AI applications in RTL code generation, hardware verification, and security enhancement, including the mitigation of hardware Trojans. The work also discusses AI-driven optimizations in power, performance, and area (PPA) metrics and the integration of AI in commercial and open-source EDA tools.

- 2. Large Language Models for EDA: From Assistants to Agents focuses on the application of LLMs in Electronic Design Automation (EDA), examining their roles as intelligent assistants and autonomous agents. It discusses how LLMs improve productivity by automating question-answering, script generation, and various design processes. It reviews cutting-edge research and practical implementations demonstrating how LLMs streamline EDA workflows, reduce manual effort, and enhance design accuracy.

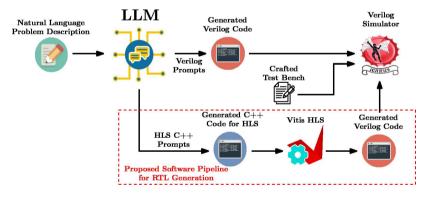

3. Evaluating Large Language Models for Automatic Register Transfer Logic Generation for Combinational Circuits via High-Level Synthesis evaluates the use of LLMs in automating RTL generation in Verilog through a two-stage High-Level Synthesis (HLS) pipeline. The authors propose an approach where LLMs generate annotated C++ code optimized for HLS, which is subsequently converted to Verilog RTL using tools like Vitis HLS. Benchmarking against the VerilogEval dataset, the study demonstrates that this two-step approach significantly improves functional correctness, achieving a pass@1 score of 0.86, outperforming direct LLM-based Verilog generation methods.

These works collectively underscore the transformative potential of AI and LLMs in revolutionizing SoC design and EDA workflows. By enhancing automation, improving security, and PPA optimizing, AI-driven methodologies pave the way for the next generation of highperformance and secure semiconductor designs. This special issue aims to provide valuable insights for researchers and industry professionals, inspiring further advancements in AI-assisted hardware design and verification.

## Deep Learning and Generative AI for Monolithic and Chiplet SoC Design and Verification: A Survey

Imed Ben Dhaou<sup>1,2</sup>, Syhem Larguech<sup>3</sup>, Sree Ranjani Rajendran<sup>4</sup>, Rajat Subhra Chakraborty<sup>5</sup>, Hannu Tenhunen<sup>2</sup> and Ahmed Abdelgawad<sup>6</sup>

<sup>1</sup>Dar Al-Hekma University, Saudi Arabia

<sup>2</sup>University of Turku, Finland; imed.bendhaou@utu.fi

<sup>3</sup>Cadence Design Systems, USA

<sup>4</sup>Florida Atlantic University, USA

<sup>5</sup>Indian Institute of Technology Kharagpur, India

<sup>6</sup>Central Michigan University, USA

### ABSTRACT

The rapid development of integrated circuit (IC) technology, driven by the growing demand for Internet of Things (IoT) devices, cloud computing, and cyber-physical systems, has introduced significant challenges in the design and verification of modern System-on-Chip (SoC) systems. Contemporary SoCs, whether used in desktops or servers, are extremely complex with billions of transistors and often use mixed-core technologies. Designing complex SoCs in modern technologies faces issues in scalability, security, verification, and design optimization, especially as the industry transitions to chipset-based architectures. In this work, we explore the potential of deep learning and generative Artificial Intelligence

Imed Ben Dhaou, Syhem Larguech, Sree Ranjani Rajendran, Rajat Subhra Chakraborty, Hannu Tenhunen and Ahmed Abdelgawad (2025), "Deep Learning and Generative AI for Monolithic and Chiplet SoC Design and Verification: A Survey", Foundations and Trends<sup>®</sup> in Electronic Design Automation: Vol. 14, No. 4, pp 245–294. DOI: 10.1561/100000063-1. ©2025 I. Ben Dhaou *et al.*  (AI) to address these challenges, focusing on applications in Register Transfer Level (RTL) code generation, design automation, hardware security, and verification.

In this work, we review the state-of-the-art in AI-driven Electronic Design Automation (EDA) tools, examining both open source and commercial platforms that have integrated AI to enhance design efficiency and performance. The work focuses on AI's role in optimizing power, performance, and area (PPA) metrics, as well as improving hardware security by mitigating threats such as hardware Trojans. In addition, we discuss the implications of adopting AI in SoC workflows and its transformative potential in democratizing hardware design.

## 1

### Introduction

The design of integrated circuits (ICs) has made significant strides in recent years, with modern System-on-Chip (SoC) architectures now containing more than six billion transistors and incorporating hundreds of mixed-core technologies. As highlighted in recent studies, this rapid advancement in IC technology is driven by the growing demand for IoT edge devices, personal augmentation systems, cloud computing, and cyber-physical systems. The proliferation of AI across edge, fog, and cloud computing has intensified the need for robust security and scalable hardware solutions.

In the era of giga-scale integration and multicore technology, circuit designers are faced with increasing challenges in thermal management, reliability, cost, and verification. To mitigate operating expenses (OPEX), semiconductor companies are adopting new methodologies emphasising design reuse and hardware intellectual property (IP) based design. However, while these approaches offer significant benefits, they also introduce new challenges in the development of secure SoCs. As reported in Bhunia *et al.* (2014), Bhunia and Tehranipoor (2017), Hussain *et al.* (2023), and Rama *et al.* (2024), the heavy reliance on third-party IPs has jeopardized the security of embedded systems. Hardware Trojan (HT) can be inserted through malicious IPs, affecting the SoC's functionality, reliability, and privacy.

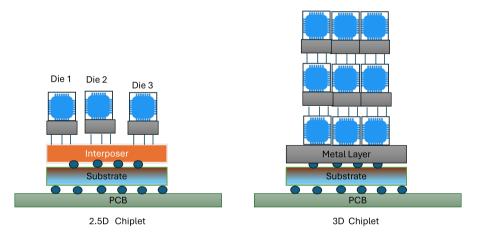

Motivated by the need to reduce cost and power consumption, monolithic SoC design has been the primary focus in integrated circuits during the last three decades commonly known as Moore's era. In the post-Moore law era, which is characterized by the integration of heterogeneous components and non-silicon technologies, chiplet-based designs are emerging as a more efficient alternative to traditional monolithic SoC (Ravikumar, 2024; Liu *et al.*, 2024). There are two common approaches for designing chiplets: 2.5D heterogeneous integration, which involves assembling multiple chiplets on an interposer, and 3D integration, which consists of stacking several dies vertically. Figure 1.1 illustrates the 2.5D and 3D heterogeneous integration approach.

Figure 1.1: 2.5D and 3D Chiplets SoC.

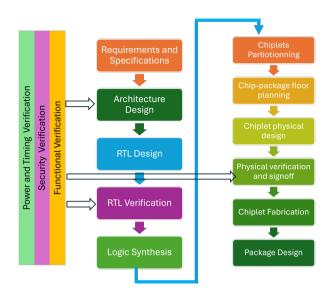

The traditional EDA design flow has been typically used to design chiplets independently. However, as suggested in Kabir and Peng (2020), early co-optimization of chiplets significantly improves system performance, signal integrity, and power efficiency compared to traditional methods where chiplets and packages are developed separately. Furthermore, EDA tools must enable secure chiplet design. The proposed secure chiplet design flow, as illustrated in Figure 1.2, involves several key stages. First, the requirements and specifications for the SoC are

Introduction

Figure 1.2: EDA design flow for designing secure SoC Chiplets.

gathered and processed. Next, these specifications are transformed into an architecture that can be described using a high-level modeling language, such as SystemC. Automated tools then convert this architecture into an RTL (Register Transfer Level) description, typically in VHDL or Verilog, which is verified through simulation. Following this, the logic synthesis phase converts the RTL design into a gate-level netlist. This list is divided into individual chiplets, each of which can be fabricated using the appropriate technology. Finally, the manufactured chiplets are assembled in the last stage of the design flow. Along the design process, after each transformation, the functionality, security, power, and timing of the design should be rigorously verified to ensure performance and security requirements are met.

The machine learning (ML) algorithms most frequently employed in the realm of SoC design and electronic design automation (EDA) tools include several notable techniques. First, reinforcement learning (RL) is particularly effective for applications that demand constant learning and adaptation to the dynamic constraints of design, such as in routing algorithms and design optimization tasks at various design abstraction levels. Next, supervised learning shows efficacy in tasks that involve identifying patterns, notably in bug detection, Register Transfer Level (RTL) verification, and ensuring hardware security. Additionally, deep learning frameworks, especially Deep Neural Networks (DNN), are capable of capturing and modeling intricate dependencies and complex relationships. These capabilities are especially beneficial in tackling issues like printed circuit board (PCB) routing and the design of chiplets.

This work seeks to explore the potential applications of generative artificial intelligence, alongside advanced deep learning techniques, in both the creation and advancement of SoC architectures, applying both monolithic approaches and chiplet-based configurations. The primary contributions of this work are enumerated as detailed below:

- This study investigates the substantial potential and impacts of deploying large language models (LLMs) within the spheres of RTL code generation, the systems inherent in design automation, and the critical verification processes that are essential to these technologies.

- It provides a comprehensive account of the various design challenges encountered in crafting monolithic SoCs alongside chipletbased architectures, with particular emphasis on challenges entailing scalability, security, and performance enhancement.

- The work meticulously examines the application of artificial intelligence-driven tools throughout various stages of design, including logic synthesis, complex physical design methodologies, and exhaustive verification procedures.

- It proposes an in-depth discussion regarding the utilization of artificial intelligence to improve strategies that enhance hardware security, focusing on methodologies aimed at reducing susceptibility to threats such as hardware Trojans and side-channel attack mechanisms.

- A detailed overview is included on the successful implementation of deep learning methods in design processes adopting the chipletbased approach.

Introduction

Generative AI, encompassing Large Language Models (LLMs) and Deep Learning frameworks, has emerged as a transformative approach to tackle the complexities of modern SoC design and verification. Generative AI systems create new content, such as RTL code or circuit layouts (Mangalagiri *et al.*, 2024), by learning patterns and structures in their training data. LLMs, such as GPT-4, specialize in understanding and generating human-like text, making them invaluable for automating tasks like code and script generation or debugging (Bengesi *et al.*, 2024). Deep Learning, a subset of machine learning, employs multi-layered neural networks to model intricate dependencies, making it particularly effective for tasks such as routing, design optimization, and performance analysis (Dong *et al.*, 2021).

This survey focuses on Large Language Models (LLMs), Deep Neural Networks (DNNs), and RL, as these are particularly well-suited for the complexities of SoC design and verification. Classic machine learning approaches, such as decision trees or clustering, are not included due to their limited applicability in addressing the high scalability and intricate dependencies inherent to SoC workflows

The rest of the work is organized as follows. Section 2 reviews existing survey works and puts our work in context. Section 3 summarizes the research work related to the design and verification of SoC systems. Section 4 describes the algorithms, tools, and techniques for large language models and generative AI. Subsequently, Section 5 discusses the application of generative AI in monolithic SoC design. Section 6 delves into the application of deep learning in chiplet design. Section 7 surveys the adoption of LLM and deep learning by EDA toolchains. Section 8 discusses the open issues in the effective use of LLM for SoC design. Finally, Section 9 concludes the work.

### **Related Work**

The inherent statistical variability of parameters in integrated circuits, such as delay, power consumption, and transistor count, has driven the adoption of machine learning, artificial intelligence, and data mining techniques for optimising, designing, and synthesizing analog, Radio Frequency (RF), and digital integrated circuits. Numerous survey papers have extensively explored this growing intersection of AI and IC design, highlighting its potential to address the challenges associated with designing and optimizing SoC systems.

The integration of artificial intelligence into integrated circuit design began four decades ago. Early examples of computer-aided design (CAD) and computer-aided manufacturing (CAM) tools include XCON, an expert system for configuring computer systems (Kirk, 1985). CMU-DA (Carnegie Mellon University Design Automation) generated technologyindependent circuit components from data flow graphs (Kowalski and Thomas, 1983), while TALIB was a knowledge-based system for automatic NMOS cell layout (Kim and McDermott, 1983). EMUCS, an extension of CMU-DA, synthesized data paths from behavioral descriptions (Hitchcock and Thomas, 1983).

The complexity of designing very-large-scale integration (VLSI) circuits, classified as an NP-complete problem, soon necessitated heuristic

Related Work

algorithms and design abstraction levels to address challenges. As detailed in Breuer *et al.* (2000), heuristic algorithms for circuit partitioning during physical synthesis include the Kernighan–Lin algorithm, Fiduccia–Mattheyses algorithm, hMetis (a multilevel partitioning algorithm), and ratio-cut partitioning. For floorplanning and placement, key heuristic techniques discussed are simulated annealing, genetic algorithms, and the quadratic placement algorithm. In the domain of Automatic Test Pattern Generation (ATPG) for single stuck-at faults (SSFs), heuristics such as the D-algorithm, Path-Oriented Decision Making (PODEM), and fan-out-oriented test generation algorithms are highlighted. Finally, fault simulation methodologies explored include concurrent fault simulation, parallel fault simulation, deductive fault simulation, and critical path tracing.

Heuristic algorithms in CAD often produce suboptimal results, as they balance performance against computational complexity. To address these limitations, machine learning (ML) has emerged as a powerful alternative. As highlighted in the survey by Rapp *et al.* (2022), ML surpasses heuristics by learning directly from data, enabling it to capture complex patterns, interactions, and dependencies inherent in modern designs. Moreover, ML leverages advanced techniques such as RL and gradient-based optimization to explore vast design spaces effectively, achieving globally optimal or near-optimal solutions. Machine learning algorithms effectively address a wide range of design challenges in the semiconductor industry, including lithography, physical design, manufacturing, yield, reliability, failure modelling, analog design, and system optimization (Elfadel et al., 2019). Specifically, machine learning algorithms have been proven to be effective in performance prediction, design space exploration, black-box design, decision-making design automation (Huang et al., 2021).

Estimating power at a high level is a crucial aspect of designing complex SoCs. For devices running on batteries, minimizing power consumption has become a vital design goal, aiming to extend the device's operational duration. The power used by the ASIC/SoC is influenced by factors such as operating frequency, switching activities, supply voltage, and switching capacitance. A variety of methods have been put forward to decrease power consumption at different stages like the system, algorithm, architecture, logic, circuit, and layout levels (Ben Dhaou, 2002; Rabaey, 2009; Reda and Nowroz, 2012). In the realm of low-power design, statistical, probabilistic, and simulation-based power estimation methods have been predominant. These techniques have been reviewed in Nasser *et al.* (2021). In the statistical approach, linear regression which is a supervised machine learning that has been widely used for developing high-level power estimation tools (Ben Dhaou and Tenhunen, 2002; Schuermans and Leupers, 2019).

In traditional machine learning, there is often a significant reliance on the extraction of features manually, along with various pre-processing steps. The scope and depth of these actions can differ substantially depending on the specific algorithm being employed and the characteristics of the dataset. However, with the remarkable progress made in the realm of cloud computing and the analytics of big data, there has been a notable rise in the application of deep learning (DL) as a particularly robust branch of machine learning. Deep learning fundamentally relies on multiple layers of artificial neural networks (ANNs) to facilitate the automatic learning of hierarchical features directly from raw data inputs. These sophisticated architectures are commonly known as Deep Neural Networks (DNNs), and they encompass specialized variants such as convolutional neural networks (CNNs) and recurrent neural networks (RNNs). These variants are particularly well-suited for complex tasks, including but not limited to image recognition applications and sequence modeling endeavors (Dong et al., 2021).

In CAD (Computer-Aided Design), deep learning is a game-changing tool with uses in synthesis, performance prediction, design exploration, run-time management, device and technology evolution, physical design, lithography, and manufacturing. For instance, convolutional neural networks (CNNs) have been employed to predict the performance of integrated circuits during high-level synthesis, enabling designers to explore vast design spaces efficiently. Similarly, generative adversarial networks (GANs) have shown promise in optimizing lithography processes by generating mask patterns that minimize defects and improve yield (Rapp *et al.*, 2022)

Many of the studies mentioned above have neglected the importance of designing secure integrated circuits, which are the foundation of trust

Related Work

in any computing-based solution. As noted in Koblah *et al.* (2023), major cybersecurity attacks such as *Meltdown* and *Spectre* exploited the vulnerabilities at the processor level. In cases where it is challenging to analytically model security properties or when multiple security conditions must be satisfied, machine learning techniques are invaluable for designing secure Computer Aided Desing (CAD) tools.

In recent years, the application of large language models (LLMs) to SoC design has gained traction. Studies such as Saha *et al.* (2024) explored their potential in hardware security, demonstrating capabilities in vulnerability insertion, security assessment, and countermeasure development. These advancements underscore the transformative role of AI in both optimizing performance and ensuring the security of modern IC designs.

### **Design and Verification of SoC Systems**

In the modern era characterized by advanced technology, there is a notable predominance of chip-centric systems. Such systems comprise devices that seamlessly integrate hardware and software components that have been meticulously pre-engineered. Collectively, these components are known in the industry as design intellectual properties, commonly abbreviated as IPs. In the present landscape, the majority of companies either independently develop these IPs through their in-house teams or opt to outsource this development to specialized external firms. When it comes to incorporating these IPs into a fully functional device, a dedicated team responsible for SoC integration takes on the crucial role. This team is charged with the careful collection and meticulous integration of the IPs, ensuring they align with the unique system requirements of the desired device. It is of paramount importance that these IPs communicate effectively amongst themselves, utilizing standardized interfaces to guarantee their successful integration into the system's configuration. For instance, the ARM AMBA bus interface provides an on-chip interconnect specification that facilitates the connection and management of various functional blocks within the system. Within the domain of SoC design, there exist two distinct verification processes: one dedicated to validating the proper functioning of the individual IPs and ensuring compliance with interface protocols, and another focused on verifying the assembled system as a whole. In contemporary times, the field of hardware verification has reached a relatively advanced stage of maturity, having been the subject of extensive study in both academic research and industrial application for at least three decades, as evidenced by numerous publications in the discipline (Bhadra *et al.*, 2007; Gupta, 1992).

In contemporary industrial practices, verification has become a key, standardized phase integrated within the systems development lifecycle. Despite the advancements achieved in technology, there remains a noteworthy disparity between the existing capabilities of state-of-the-art verification techniques and the demands imposed by contemporary industrial design practices. The dynamic evolution of the design landscape further intensifies these challenges as we transition swiftly and perhaps inevitably into an era characterized by autonomous vehicles, the proliferation of smart cities, and the expansive growth of the Internet of Things (IoT). This profound shift has heralded the advent of an environment wherein electronic devices ubiquitously gather, analyze, and securely store vast amounts of our most personal and private information, such as geographic location, health data, fitness metrics, and sleep cycles. After this information is transmitted across a global network comprised of billions of interconnected computers, the system remarkably sustains uninterrupted operation, even in the presence of millions of potentially malicious or compromised nodes within that network. Therefore, it is crucial that verification processes evolve in tandem with the design and architectural frameworks of these systems to effectively integrate within this novel ecosystem (Ray et al., 2016; Farahmandi et al., 2023a; Nath et al., 2018; Rajendran, 2020).

The availability of resources is a highly significant factor influencing the verification process in contemporary times. The imperative to manufacture vast quantities of varied computing devices has intensified the constraints on time to market for both design and system development. Historically, the typical life cycle of a microprocessor—from the exploratory phase to the commencement of production—spanned approximately three to four years. Conversely, the life cycle duration for certain Internet of Things (IoT) devices has now been truncated to less than one year (Chen *et al.*, 2017).

Due to this accelerated contraction, there is inadequate time available for comprehensive design evaluations, which can lead to misunderstandings between developers and stakeholders concerning the design's functional decomposition. This, in turn, elevates the risk of errors. Additionally, a condensed life cycle allows for reduced testing duration. Verification teams are consequently tasked with managing designs that may be more prone to errors using limited resources and in a constrained timeframe. Such aggressive scheduling has resulted in an increase in infield escapes and a heightened demand for post-deployment patches on devices and systems, often necessitated through updates to software and firmware. Moreover, the creation of verification methodologies targeting feasible and highly valuable objectives, including security, networking, and cyber-physical elements, has become imperative.

The increasing complexity of contemporary computing devices necessitates meticulous planning from the outset, which extends through nearly the entire design lifecycle. The process of verification planning is initiated simultaneously with the commencement of product planning and persists throughout the entirety of the system development phase (Chen et al., 2017; Rajendran, 2020). Within the framework of product planning, it becomes essential to delineate the diverse Intellectual Properties (IPs) needed, as well as their breakdown into both hardware and software constituents. This process involves specifying the interfaces required for interconnection and seamless communication. Additionally, it is crucial to establish and understand the variety of objectives concerning power consumption, system performance, security, and energy efficiency. As a result, the phase of verification planning encompasses the development of detailed test plans and corresponding test cards, alongside the generation of Verification IPs (VIPs). These Verification IPs represent specialized blocks within the design that play a critical role in debugging activities following the silicon fabrication. Furthermore, the design incorporates instrumentation that is integral to the processes of monitoring, checking, and actively exercising the system.

System architecture is a critical aspect of defining an SoC design, as it establishes the functional parameters, communication protocols among IPs, and the schemes for managing power and performance. This phase involves an in-depth examination of numerous parameters and design characteristics, such as cache size, pipeline depth, and protocol specifications for security and power management. During this exploration, various "architectural models" are employed to simulate typical workloads and the intended use cases of the device, thus helping to determine parameters that meet the objectives set in the planning phase, which often includes considerations like power, performance, and security. At this juncture in the architectural exploration process, two primary verification activities are paramount (Rashinkar et al., 2007; Lee and Kim, 2011; El Fentis, 2020). The initial activity involves ensuring that all communication protocols function as anticipated. By engaging in this process early, when the design models are abstract and the overall design is still nascent, high-level protocol errors can be detected early, leading to reduced costs; if such errors are discovered later in the product implementation, resolving them might necessitate a significant redesign of multiple IPs.

Due to the abstract nature of design models at this phase, formal analysis is employed to meet this goal. In conjunction with formal analysis, high-level simulation is utilized in practice to obtain the necessary coverage (Talupur *et al.*, 2015). Besides its indispensable contribution to software and firmware verification, verification is instrumental in commencing the creation of hardware prototyping models. This requirement arises because the low-level software and firmware programs must be validated to function correctly alongside the target (and evolving) hardware design developed during the implementation phase. Nevertheless, the verification of software and firmware must proceed without waiting for the hardware implementation to stabilize. Consequently, high-level hardware-software models are generated to expedite the verification process for software and firmware.

The process of formal verification of SoC connectivity typically involves representing specifications in spreadsheets or XML documents. Once these specifications are loaded, the dedicated software tool autonomously generates the properties necessary to carry out formal verification (Liao and Hsiung, 2003). This approach, however, brings about the challenge of establishing a standardized specification framework

capable of encapsulating the myriad of available connection schemes. Furthermore, the intricacy involved in administering the verification process for an extensive number of properties—running into tens of thousands—can be daunting, often necessitating the parallel operation of formal verification engines across a distributed computing environment. In addition to formalizing the connectivity verification as per an existing specification, there exists an additional utility that is adept at extracting and retrieving high-level connectivity specifications from a given design, in instances where no formal specification is provided (Farzana et al., 2019). The design specifications can subsequently be reviewed based on these extracted specifications. Moreover, it is a typical scenario wherein SoC designs undergo modifications aimed at enhancing performance or features, with the connectivity remaining unaffected. Hence, the extracted specifications serve as a valuable resource for formally verifying whether such design modifications have maintained connectivity integrity.

Within an SoC architecture, IP blocks comprise numerous memorymapped registers that can be accessed by system or user-level software to configure the IP and monitor its operational state. Relative to other system components, these memory-mapped registers exhibit a lower complexity in terms of implementation. However, due to the vast number of registers, each governed by distinct access protocols, verifying them manually using directed or slightly random tests is a labor-intensive and error-prone process, as stated by Kim *et al.* (2013). This challenge is further exacerbated by sophisticated features like register aliasing and remapping, which introduce additional layers of complexity. Verifying memory-mapped registers is also hindered by the lack of precise and dependable specifications; specification documents occasionally overlook critical details, such as scenarios where a memory-mapped register might be internally altered (Kim et al., 2013; Roy, 2007; Liao and Hsiung, 2003). In circumstances where behavior is undocumented, verification engineers are often compelled to resort to trial and error methods to ascertain this behavior.

Due to the increasing complexity and integration of SOC, its development time increases dramatically, and its verification time even more so. As part of the verification process, many directed or randomized

### Design and Verification of SoC Systems

simulation tests are generated and run as regression tests. As far as full chip verification goes, this regression could represent a critical path in a project's schedule if it takes a considerable amount of time to complete. A machine learning (ML) model was useful in automating many parts of the process, which occupied engineers' time and distracted them from adding new coverage metrics. A variety of machine learning models are currently being deployed in areas such as stimulus constraining, test generation, coverage collection, bug detection, and localization (Vaithianathan et al., 2024). By combining AI and Machine Learning with Universal Verification Methodology (UVM), semiconductor design has been thought to become more efficient and accurate. The most effective applications of AI and ML are those concerned with automating timetapping processes that were previously subject to human error. Using these technologies, it is possible to sift through a huge volume of data and identify what the algorithm believes is likely to be weaknesses in a design not easily noticeable by humans. In addition to supporting the verification task, it also improves the quality of the verification result.

Detecting bugs in software at the Register Transfer Level (RTL) level through a novel AI-driven approach is proposed in Wang et al. (2024a). By combining advanced machine learning techniques with domain-specific knowledge of chip design, we address the challenges of increasing complexity and deadline pressures in modern integrated circuits. A comprehensive preprocessing pipeline captures the syntactic and semantic features of RTL code and feeds it into a novel attention-based neural network model. There are still a number of major challenges facing formal verification despite impressive advances. Modeling the environment, insufficient specifications, and complex decision problems are among the most significant. Inductive inference (learning from examples) using hypotheses about system structure is a viable method of tackling these challenges (Seshia, 2012). Researchers (Farahmandi et al., 2023b) examined the benefits of machine learning, inferred new relationships between side-channel measurements, and extracted sensitive data in the survey. The survey also focuses on techniques used to detect and prevent malicious attacks in machine learning systems. Furthermore, it seeks to identify challenges associated with using machine learning for security purposes. In Hughes *et al.* (2019), two DUTs were

tested using both reinforcement ML algorithms and supervised learning algorithms. Constrained-random DV environment tools are leveraged by using supervised learning and reinforcement learning techniques to enhance them. In this way, Design Verification (DV) objectives of full design coverage are achieved on an accelerated timescale and with fewer resources than randomly generated results. Here are two hardware verification examples based on open-source RISCV-Ariane design and Google's RISCV Random Instruction Generator: one using a Cache Controller design and the other using an open-source RISCV-Ariane design.

Employing formal methods to verify records offers the possibility of automating the traditionally manual procedure of analyzing access policies. This is achieved through the formulation of formal properties concerning these policies and subsequently verifying their accuracy and integrity using formal methodologies. The principal challenge encountered in this context is the creation of thorough and robust assumptions about access policies, especially in relation to their application to advanced functional aspects (Grimm *et al.*, 2018).

While classic ML algorithms, such as k-means clustering and support vector machines (SVMs), have been explored in hardware design, they often fall short in tasks requiring scalability and adaptive learning, such as routing and design optimization. This survey emphasizes modern algorithms like LLMs, RL, and DNNs, which better address these challenges.

### Overview of Generative AI and Large Language Model

Natural Language Processing (NLP) is an important field in computer science and artificial intelligence which lies at the intersection of computational linguistics, statistical engineering, and human language. It has evolved from simple tasks, such as translation in the early 1960s, to solving more complex problems, driven by Large Language Models (LLMs).

LLM represents a category within generative artificial intelligence, often abbreviated as GenAI. While LLMs primarily focus on producing human-like text, GenAI encompasses a broader spectrum of capabilities. Beyond text generation, it can create a variety of other media formats. These include the production of visual media such as videos and images, as well as auditory outputs like speech (Bengesi *et al.*, 2024).

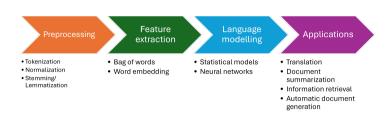

Typical NLP applications include virtual assistant text summarization, sentiment analysis, information retrieval, and speech recognition. As shown in Figure 4.1 a typical NLP chain consists of four main stages. In the first stage, the text or corpus is pre-processed. In the second stage, the features of the document are extracted. In the third stage, the language of the document is modeled. Finally, the last stage performs the intended task on the document.

Figure 4.1: NLP processing blocks.

Language modeling (LM) plays an instrumental role in the design of effective NLP tasks. Earlier techniques such as *N*-gram models have been based on probabilistic theory, in which it predicts the next word,  $w_n$ , given the history  $(w_1, w_2, \ldots, w_{n-1})$  using conditional probability  $P(w_n \mid w_1, w_2, \ldots, w_{n-1})$  (Chang *et al.*, 2024). The N-gram model is computationally efficient and requires processing a corpus to compute the probabilities. However, its precision is limited by the number of words *n* used to compute the probability, making it unable to capture long-term dependencies in the text. Furthermore, the N-gram model suffers from both sparsity and storage problems.

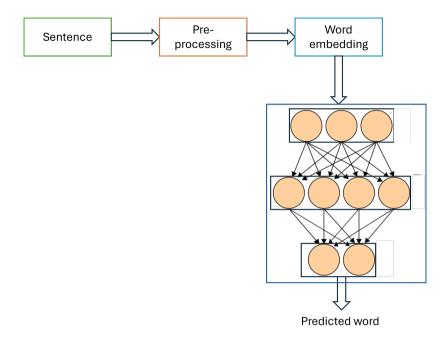

Neural networks (NN) and their variants, such as Recurrent Neural Networks (RNN) and Long Short-Term Memory (LSTM) networks, have replaced the N-gram model, ushering in a new era of language modeling. As illustrated in Figure 4.2, words or tokens are first converted into word embeddings using algorithms that produce vectors in a high-dimensional space, capturing the semantic relationships between words. These vectors are then fed into the input layer of the neural network. The hidden layers process the embeddings, and the output layer generates the final predictions.

Neural network (NN)-based architectures have significantly transformed language modeling, laying the foundation for advanced techniques in natural language processing (NLP), particularly in tasks such as neural machine translation (NMT) and named entity recognition (NER). The introduction of NNs, particularly recurrent neural networks (RNNs), enabled breakthroughs in sequence processing, while the development of word embeddings provided a method to represent words as continuous vectors in semantic space, capturing relationships Overview of Generative AI and Large Language Model

Figure 4.2: Architecture of a neural network-based language model.

between words through vector similarity. However, a key limitation of early NN-based translation models, such as those using RNNs, is their reliance on fixed-length vector representations to encode input sequences. This constraint can lead to information loss in long sequences and impose computational inefficiencies, particularly when dealing with long or complex sentences.

The attention mechanism, proposed as a solution to this limitation, allows models to selectively focus on relevant parts of the input sequence while generating each output token (Bahdanau *et al.*, 2015). This solution addressed the bottleneck of fixed-length vectors and improved both accuracy and computational efficiency. The chief idea is the dynamic assignment of different weights to different input tokens based on their relevance to the current prediction. Despite these improvements, attention-based models that still rely on RNNs face challenges, notably high memory consumption and slower training times. To address these issues, the *Transformer* architecture was introduced in 2017, replacing RNNs entirely with attention mechanisms. The Transformer, composed of an encoder-decoder architecture, uses multi-headed self-attention and feed-forward neural networks to process sequences in parallel, drastically improving both sed and scalability. The encoder consists of layers of multi-headed self-attention and feed-forward networks, while

the decoder incorporates masked multi-headed self-attention to handle autoregressive generation. This technique, known as the Transformerbased architecture, created another inflection point in NLP (Vaswani *et al.*, 2017).

As summarized by Zhao *et al.* (2023), scaling laws relate the performance and efficiency of LLMs to the model size  $(N_M)$ , the number of tokens  $(N_D)$ , and the computation cost during training  $(N_C)$ . The two most widely used formulas for estimating the performance of LLMs are the KM scaling law and the Chinchilla scaling law, which are capable of estimating the performance of LLMs given  $N_M$ ,  $N_DS$ , and  $N_C$ . In their original article, Kaplan *et al.* (2020) found that the scaling law is weakly dependent on the network depth and size. Using the cross-entroy loss (L), the expression for the KM scaling law is given in (4.1-4.3). Those equations are valid for model size in the range of 768 million to 1.5 billion non-embedding parameters and the data size in the interval 22 million to 23 billion tokens.

$$L(N_M) = \left(\frac{N_c}{N_M}\right)_{NM}^{\alpha} \tag{4.1}$$

$$L(N_D) = \left(\frac{D_c}{N_D}\right)_{ND}^{\alpha} \tag{4.2}$$

$$L(N_C) = \left(\frac{C_c}{N_C}\right)_{NC}^{\alpha} \tag{4.3}$$

The fitting values for  $N_c, \alpha_{NM}, D_c, \alpha_{ND}, C_c$  and  $\alpha_{NC}$  are summarized in Table 4.1.

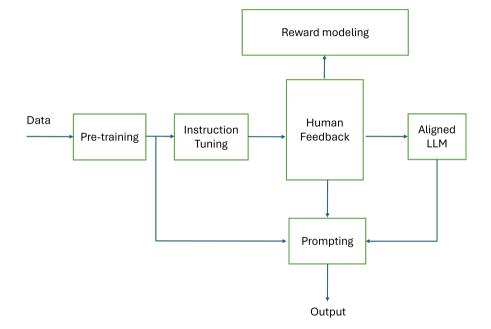

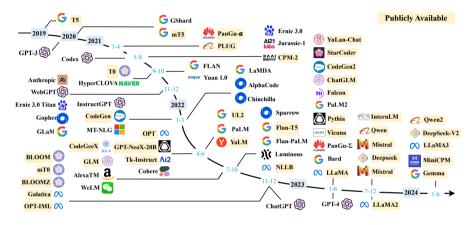

The emerging capabilities of LLMs have been shown to be predicted using these scaling laws, including in-context learning, instruction follow-up, and step-by-step reasoning. The general architecture of LLMs, depicted in Figure 4.3, illustrates the essential operations involved in LLM (Naveed *et al.*, 2023). The architecture includes blocks dedicated to in-context training, which allows the model to adapt and respond

#### Overview of Generative AI and Large Language Model

| Parameter     | Fitting Value                         |

|---------------|---------------------------------------|

| $N_c$         | 88 trillions non-embedding parameters |

| $\alpha_{NM}$ | 0.076                                 |

| $D_c$         | 54 trillions tokens                   |

| $\alpha_{ND}$ | 0.095                                 |

| $C_c$         | $3.110^8$ PF-day                      |

| $\alpha_{NC}$ | 0.05                                  |

Table 4.1: Summary of fitting values for various parameters.

Figure 4.3: Generic architecture of LLM with prompting and reward.

based on the context provided within the input data. Furthermore, the architecture incorporates mechanisms for improvement through *Rein-forcement Learning with Human Feedback* (RLHF), where the model's performance is iteratively improved based on feedback from humans. The prompt block guides the operation of the LLM by providing specific instructions or contexts that the model uses to generate relevant and coherent responses.

### Applications of Generative AI in SoC Design

Prior to the development of large language models (LLMs), neural network-based natural language processing (NLP) techniques were widely adopted in tasks such as automatic software development, software testing, and bug fixing for both embedded systems and generalpurpose computing (Hai *et al.*, 2022). As highlighted in a survey by Dehaerne *et al.* (2022), popular applications of machine learning in automatic software development include code generation from natural language specifications, software documentation, automatic program repair, and programming by example. The survey also emphasized that transformer-based models significantly outperform earlier architectures like recurrent neural networks (RNNs) and convolutional neural networks (CNNs) for tasks involving code generation from natural language specifications. This is largely due to the transformers' ability better to capture long-range dependencies and contextual relationships in code, making them more effective for complex programming tasks.

Earlier approaches for automatic software development had limited capabilities in handling complex and context-rich tasks. In contrast, large language models have demonstrated impressive performance in software engineering. For example, Codex, a fine-tuned generative pretrained transformer developed by OpenAI, can generate standalone Python functions from docstrings which is a string used to document a Python function, class, module, or method (Chen *et al.*, 2021). Codex is used in GitHub Copilot (OpenAI, 2024).

Stemmed by the success in code generation, recently, LLMs' capabilities have been extended to cover SoC design. As summarized in Wang *et al.* (2024b), LLMs have been used in EDA and hardware security. In the EDA realm, LLMs are used, for instance, for RTL code generation, design optimization, bug fixes, script generation for HLS tasks, HDL verification, and analyses (Wu *et al.*, 2024a). For hardware security, the applications of LLMs include fixing hardware security bugs, inserting Hardware Trojan (HT), defending against side-channel attacks, and generating security assertions.

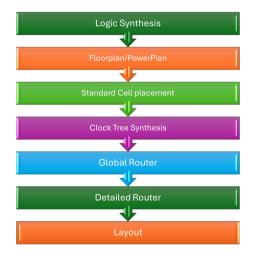

With the objective of democratizing hardware design, the Open-ROAD project, an open-source EDA toolchain, has been initiated. The tool is capable of performing logic synthesis and physical design tasks, including floor planning, clock tree synthesis, and global and detailed routing. The OpenRoad design flow is described in Figure 5.1. It combines both logic and physical synthesis. The tool generates GDSII file given the RTL description of the circuit using Verilog hardware description language (Ajayi *et al.*, 2019).

Figure 5.1: openROAD design flow.

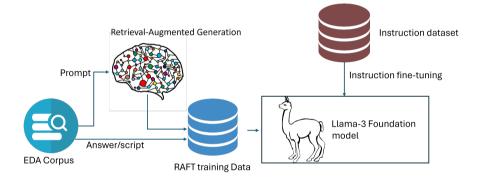

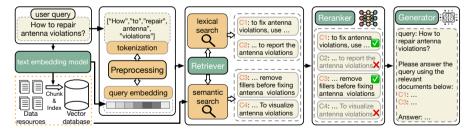

To further enhance the capabilities of the OpenROAD toolchain, an open-source curated dataset for training large language models has been created. The dataset is designed to generate scripts and answer questions through a tailored chatbot. The question-answer dataset has been collected from the OpenROAD GitHub and is categorized into three groups: general questions pertaining to the use of OpenROAD, specific questions on OpenROAD tools, and questions on the design flow of OpenROAD from RTL to GDS. The dataset has been used to develop an open-source LLM-powered chatbot using the Llama3-8B foundation model. The training process is pictured in Figure 5.2.

Figure 5.2: Training process for the OpenRoad-assistant reported in Sharma *et al.* (2024).

The process is initiated by sending queries to the retriever model, which searches through a domain-specific database. The context retrieved is merged with the supervised training data to form a RAFT (Retrieval Augmented Fine-Tuning) dataset. The Llama3 foundation model is then trained using the new RAFT dataset. Compared with ChatGPT-3.5, ChatGPT-4, Code Llama, and Claude3, the OpenROAD-Assistant scored high in script generation (77% pass@1 and 80% pass@3) and in question-answering tasks (98% BERTScore and 96% BARTScore).

The work presented in Chen *et al.* (2024) explores the shift from traditional AI-enhanced Electronic Design Automation (AI4EDA) towards AI-native EDA systems, driven by the development of Large Circuit Models (LCMs). The authors argue that existing AI4EDA solutions, which repurpose models from domains like vision and language processing, are insufficient for the unique complexities of circuit design. Instead, they propose LCMs—multimodal models tailored to EDA workflows that can unify diverse design stages such as specification, RTL, netlists, and physical layouts.

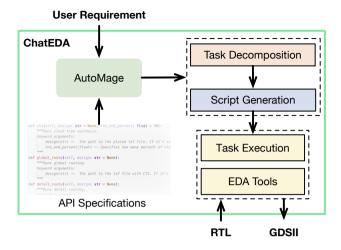

Motivated by the need to have a specialized LLM for automating the design of SoC, the work by Wu *et al.* (2024b) elaborates on an autonomous agent named ChatEDA, which uses a fine-tuned open-source LLM model, Llama2. The agent, AutoMage, is capable of autonomously decomposing tasks, generating scripts, and executing tasks. The work details the integration of EDA tools to streamline the design flow from RTL to GDSII. The capabilities of AutoMage have been compared with existing foundation models such as GPT-3.5, Claude2, and GPT-4, demonstrating superior performance in handling EDA tasks. Additionally, an upgraded version, AutoMage2, incorporates enriched training data, instruction tuning with explanations, and chain of thoughts prompting to further enhance its capabilities.

# 6

## AI Techniques for Chiplet Design and Heterogeneous Integration Packaging

The semiconductor sector is transitioning significantly from traditional monolithic chips to the arena of three-dimensional integrated circuits (3D-IC), chiplets, as well as vertically stacked silicon and wafers. Presently, advanced SoCs are encountering the constraints imposed by reticle size limits. Many enterprises have come to the consensus that solely adhering to Moore's Law, often referred to as "More Moore," no longer represents the most viable path forward in terms of both technical and economic aspects, especially for the upcoming generation of designs. As the industry approaches the finite scaling limits inherent to advanced nodes, the pressure for enhanced computational performance along with efficient data transfer has reached unprecedented levels. This scenario has necessitated the exploration and development of pioneering solutions, aiming to maintain the trajectory of Moore's Law scaling while achieving notable improvements in performance, coupled with a reduction in power consumption.

The semiconductor packaging sector is gearing up to assume a more prominent and essential role in the design of future electronic products. The integration of chips through vertical stacking within a single package (known as 3D integration) and the employment of a

#### AI for Chiplet Design and Heterogeneous Integration Packaging

multi-chiplet structure utilizing a silicon interposer within the same package (referred to as 2.5D integration) are becoming favored solutions, each presenting distinct challenges. As the demand for heterogeneous chiplet-based architectures increases, there is a necessity to develop innovative system-level design methodologies that focus on optimizing Power, Performance, and Area (PPA) metrics at the system level. The Cadence Integrity 3D-IC platform stands as the industry's pioneering comprehensive solution for system planning, execution, and precise preliminary analysis. This platform makes use of Cadence's leadingedge implementation and validation technologies across digital, analog, and packaging domains, all coordinated within a cohesive hierarchical database.

In the context of heterogeneous integration, an IC package now includes various elements such as bare dies/chiplets, packaged devices, interposers, bridges, and passive components. Numerous complex IPs must be routed within the package, including die-to-die connections and links between dies and SMD components to the board, such as DDR, PCIe, and UCIe. A range of strategies must be explored to find the optimal routing solution, which can be time-consuming. The chosen strategy will directly affect the routing quality of both the IC package and the board, as well as the overall system cost. AI approaches have demonstrated their ability to outperform humans in problems requiring multiple strategies to win.

In the design flow, many advanced routing algorithms are adopted to automatically route all nets. Physical design routing was traditionally solved using heuristics and optimization. Below is an example of some work related to physical design routing.

The algorithms are classified into escape routing and area routing. Escape routing is more complex to achieve compared to area routing because of the high routing density. It is an important problem in package and PCB design. Several works were conducted to develop escape routing solutions mainly for PCB designs. Network flow (Yan and Wong, 2012) and nonflow (Gandhi *et al.*, 2019) are pervasively used to model this problem. The proposed escape routing models are classified into three categories; unordered escape (Yan and Wong, 2012) (Chen *et al.*, 2023), ordered escape (Lin *et al.*, 2021) and simultaneous escape (Ozdal and Wong, 2004).

For instance, the DDR macro is considered the most complex IP to escape route in IC package design. It often determines the required total number of layers of the substrate. For this macro type, net grouping is needed, requiring an ordered escape routing approach with significant consideration given to power and ground connections. Each of the above methods has limitations, such as not considering different net types (power, ground, and Differential Pairs (DP)) or net ordering. Crosstalk is a major issue for DDR macro routing. To achieve the IP's requirements in terms of crosstalk values, adjusting the line spacing outside the escape region is often a key element. The line spacing outside the escape routing region also influences the escape routing strategy. The more severe the crosstalk requirements, the larger the spacing between the lines both outside and inside the macro.

In the study outlined in Yu and Wei-Ming Dai (1995), the authors present a pioneering routing framework known as the Alpha-PD-Router, which is underpinned by a RL methodology that is independent of specific data architectures. This model is adept at learning to route circuits while simultaneously resolving short violations. The underpinning RL strategy, named Alpha-Go Zero, distinguishes itself by negating the necessity for extensive training datasets, which are notoriously challenging and costly to compile. Rather than relying on such datasets, this approach empowers an RL agent to acquire routing efficiencies and improve routing strategies through dynamic interactions within the design environment. The designed Alpha-PD-Router leverages a sophisticated cooperative min-max game framework synergistically integrated with physical design routing algorithms. This novel framework derives its conceptual foundation from the principles of Alpha-Go Zero, an innovation by Google that has demonstrated the capability to master the intricate game of Go autonomously, without human guidance.

The work presented by McMurchie and Ebeling (1995) introduces a comprehensive routing algorithm designed to address a variety of complex, real-world constraints essential for effective printed circuit board routing. For this routing task (including Signal, power, and ground distribution, and DP), the Pathfinder algorithm (Fang *et al.*, 2009), known for its negotiation-based approach, is utilized. This algorithm aims at minimizing violations of design rules while achieving comprehensive

#### Full text available at: https://nowpublishers.com/EDA

34

#### AI for Chiplet Design and Heterogeneous Integration Packaging

routing solutions. Notably, the pathfinder is capable of executing both escape routing and area routing operations. Originally devised for routing circuits on FPGAs, Pathfinder functions as an iterative algorithm adept at managing and reconciling the conflicting objectives of reducing congestion and minimizing the delay across critical paths within an iterative process. This process begins by permitting signals to utilize shared routing resources but transitions into a phase where signals must negotiate to ascertain which requires the shared resources the most. The authors further suggest an innovative cost function specifically designed for managing obstacles encountered by routed nets during each iteration of the routing process.

The core innovation of Fang *et al.* (2007) involves the use of non-local criss-cross attention networks, a type of neural network architecture that captures long-range dependencies and spatial relationships more effectively than traditional methods. This allows the model to consider thermal effects across the entire PCB layout, rather than just local areas. The criss-cross attention module enables the network to focus on critical areas that influence thermal distribution, allowing for more informed routing decisions. The model incorporates thermal metrics directly into the routing optimization process, using data on thermal conductivity, power dissipation, and other relevant factors. The authors use a comprehensive dataset of PCB designs, including thermal simulations and routing solutions, to train and evaluate the T-Router model. Performance is assessed using metrics such as thermal uniformity, routing efficiency, and computational time. The thermal-driven routing approach shows high efficiency in achieving a low-temperature PCB design compared to the classic verification-then-fix approach.

# 7

## Adoption of Generative AI and Deep-learning by Open Source and Commercial EDA Tools

Leading Electronic Design Automation (EDA) companies have been expanding their capabilities by integrating AI and generative AI technologies into their toolsets. The following section explores this significant surge and its impact on the evolution of EDA solutions.

#### 7.1 Cadence Design Systems

The Cadence Joint Enterprise Data and AI (JedAI) platform is designed to accelerate intelligent design processes from chips to complete systems. It features a variety of generative AI applications, including Allegro X AI, Optimality Intelligent System Explorer, Verisium AI-Driven Verification, and Cadence Cerebrus Intelligent Chip Explorer (Cadence Design Systems, 2025).

Allegro X AI utilizes cloud scalability to significantly reduce PCB design cycle times. By automating component placement, power plane creation, and critical net routing, it boosts engineers' productivity. This allows for more iteration and exploration without sacrificing quality, ensuring electrical correctness and manufacturability.

The Cadence Optimality Intelligent System Explorer facilitates the analysis and optimization of electronic systems, transcending traditional, Full text available at: https://nowpublishers.com/EDA

Adoption of Generative AI and Deep-learning

labour-intensive optimization processes. It replaces the conventional design-test-refine loop with generative AI technology, quickly delivering optimal system design solutions without compromising accuracy. Additionally, Cadence Cerebrus Intelligent Chip Explorer offers an AI-driven, automated approach to chip design flow optimization. Block engineers define design goals, and the generative AI features intelligently optimize the design to meet power, performance, and area (PPA) objectives in a fully automated manner.

Moreover, the Cadence Verisium AI-Driven Platform represents a significant leap forward by harnessing big data and generative AI across multiple runs of multiple engines in a comprehensive SoC verification campaign. Verisium optimizes verification workloads, enhances coverage, and accelerates root-cause analysis of bugs. Cadence Virtuoso Studio, a key component of the Cadence.AI Generative AI Platform, builds on 30 years of industry expertise in custom/analog design, extending support to systems including RF, mixed-signal, photonics, and advanced heterogeneous designs. Innovative AI techniques, cloud enablement, infrastructure improvements, and seamless integration across Cadence products further streamline these design flows, creating an efficient hub for delivering real-world designs.

In a significant advancement, Cadence is rolling out its inaugural robust demonstration of a large language model (LLM) tool tailored for chip design, named Cadence ChipGPT. This innovative LLM is particularly advantageous in the design-cleanup phase, allowing engineers to cross-verify designs against specifications, diagnose and rectify potential discrepancies, and initiate analytical tasks with comprehensive explanations in human-readable language. This sophisticated tool facilitates various review processes, conserves substantial engineering hours, and diminishes the frequency of extensive group discussions. Additionally, it plays a critical role in detecting numerous bugs that may elude identification prior to regression verification (Freund, 2023).

The proof-of-concept for Cadence's ChipGPT signifies the commencement of a potentially protracted journey towards implementing large language models (LLMs) in the sphere of chip design. Nevertheless, those clients leveraging the JedAI platform have already demonstrated remarkable outcomes through this initiative, achieving a substantial

#### 7.2. Siemens EDA Software

reduction in the time needed to transition from initial specifications to final designs while simultaneously improving the degree of design control.

Cadence emphasizes data security in scenarios where AI algorithms need to interact with sensitive intellectual property. The implementation of Cadence's LLM is conducted wholly on-premises, ensuring that all data is securely stored and managed within the confines of the Cadence.AI platform, safeguarded by the enterprise's firewall. The LLM's computational operations are executed on the server infrastructure provided by the customers, which can be based on either CPU or GPU architectures.

#### 7.2 Siemens EDA Software

The company offers a full suite of EDA tools for designing PCBs, integrated circuits, and packaging. According to Siemens (2023), the integration of AI into its EDA tools began in 2018, driven by a shortage of experienced design engineers and the need to reduce time-to-market. AI has been deployed to automate various IC design processes, ensuring correct-by-design hardware and significantly improving design efficiency and accuracy.

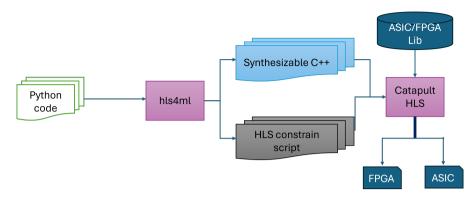

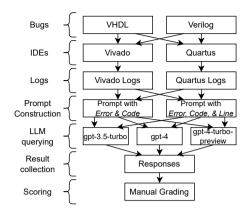

The high-level synthesis and verification tool, Catapult, automatically transforms a SoC described in SystemC or C++ into a PPAoptimized RTL description. To enhance designer productivity, Catapult AI uses machine learning to convert Python code into designs for neural network (NN) hardware or AI accelerators. The design flow for Catapult AI NN is shown in Figure 7.1.

#### 7.3 Synopsys EDA Software

Synopsys offers a wide range of EDA tools for designing monolithic SoCs and chiplet-based SoCs. It also provides access to its EDA toolchain through Software as a Service (SaaS) via cloud computing. The Fusion Design Platform is accessible through a hybrid cloud model. The platform uses AI to analyze and optimize design parameters and to automate intricate design tasks.

Figure 7.1: Design flow of Catapult NN.

| Application | Description                                                               |

|-------------|---------------------------------------------------------------------------|

| VSO.ai      | AI-based verification space optimization                                  |

| DSO.ai      | Design space optimization AI                                              |

| Design.da   | End-to-End AI-driven data analytics platform                              |

| TSO.ai      | AI-driven autonomous system for ATPG configuration and QoR optimization   |

| Silicon.da  | A comprehensive data analytics solution from design through manufacturing |

| Fab.da      | Comprehensive AI-driven process analytics and control solution            |

Table 7.1: Summary of Synopsys AI solution.

The company has a full stack of AI-driven EDA tools that span system architecture, design, and manufacturing. AI in the toolchain is used to optimize the design, data analytics, and generative AI. Generative AI facilitates the use of the EDA tools, better analyses reports, and streamlines workflows. It is also used to reduce the time spent on developing RTL and in the universal verification methodology. Figure 7.2 summarizes the use of generative AI, machine learning, and data analytics solutions in Synopsys's design tools. These solutions are summarized in Table 7.1.

#### 7.4 Start-up AI EDA Companies

An unprecedented increase in the emergence of startup enterprises, often referred to as AI EDA firms, has been significantly driven by recent progress in artificial intelligence technologies.

#### 7.4. Start-up AI EDA Companies

| System Architecture                     | End-to-end workflow creation from natural language using<br>Generative Al                                           |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Design capture                          | Shorten development time of RTL and formal verification assertions                                                  |

| Verification                            | Uses ML and AI to enhance verification coverage, optimize test runs, and perform root cause analysis                |

| Implementation                          | Uses reinforcement learning for PPA optimization                                                                    |

| Signoff                                 | Leverages ML for signoff closure by collecting and analyzing data collected throughout the design flow              |

| Test and Silicon Lifetime<br>Management | Leverages data analytics and AI to optimize test patterns identify and fix issues in the semiconductor supply chain |

| Silicon manufacturing                   | Uses AI to improve yield and performance                                                                            |

Figure 7.2: Integration of Generative AI, ML, and data analytics in Synopys's toolchain.

The company Primis AI (2025) has developed an AI-driven EDA tool known as RapidGPT. This tool greatly aids engineers by providing capabilities to write, optimize, and troubleshoot HDL code with elevated efficiency. RapidGPT extends support to VHDL, Verilog, and SystemVerilog languages. Additionally, the tool is equipped with a Retrieval Augmented Generation (RAG) database, which is a significant asset for hardware designers seeking to integrate intellectual properties (IPs) within their design processes.

Silimate, established in 2023, represents another emerging company in the field of AI-driven electronic design automation (EDA). The firm is actively working on bringing to market a co-pilot tool designed to assist designers in crafting Register Transfer Level (RTL) code that is both free from bugs and optimal in terms of power, performance, and area (PPA) efficiency (Silimate, Inc., 2025).

### Discussions

The integration of deep learning and generative AI into SoC and chipletbased designs is rapidly transforming the landscape of hardware design and verification. This work has demonstrated the potential of these technologies in addressing some of the most critical challenges in design scalability, performance optimization, and hardware security. In particular, the application of AI-driven EDA tools like Siemens' Catapult, Cadence Cerebrus, and the emerging OpenROAD-Assistant illustrates how AI can enhance traditional design workflows, improving time-tomarket and reducing the complexity of verification processes.

One of the most significant contributions of AI is its ability to optimize RTL code generation, physical design, and logic synthesis through automation. By leveraging machine learning models, tools can now handle vast design spaces, offering design space exploration with a level of efficiency that manual processes cannot match. AI-driven optimizations have shown promise in achieving improvements in power, performance, and area (PPA) metrics, making them particularly valuable in the era of heterogeneous chiplet architectures. For example, the use of deep learning for routing algorithms in chiplets, as discussed, has the potential to streamline complex design constraints while minimizing signal integrity and thermal issues. Despite the progress, several challenges remain. One of the most critical issues is the interpretability of AI models in hardware design. While large language models (LLMs) and deep learning algorithms can optimize design processes, the lack of transparency in how decisions are made can be problematic, especially in security-critical applications. Explainable AI approaches will need to be integrated into the design flow to ensure that engineers can understand and trust AI-generated

Another challenge is the scalability of AI models, particularly when applied to increasingly complex SoC architectures. As chiplets and 3D-IC designs become more widespread, AI models must scale efficiently to handle the larger datasets and more intricate design requirements. Furthermore, integrating AI-generated designs into existing workflows, especially in environments with legacy systems, poses another hurdle. Ensuring compatibility and seamless integration with traditional EDA tools will be key to broader adoption.

solutions.

In the process of validating Verilog designs, Large Language Models (LLMs) have exhibited significant potential in automating the generation of test stimuli. For example, LLMs have successfully generated test cases for simple combinational and sequential circuits. Nevertheless, the reliability of LLMs in verifying more complex designs, such as those with extensive concurrent processes and intricate module hierarchies, remains a challenge. This domain still demands additional exploration and detailed study. Future research should focus on enhancing LLMs' comprehension of large-scale Verilog code and integrating them with other AI techniques, such as Graph Neural Networks (GNNs), to improve their scalability and accuracy (Ma *et al.*, 2024).